# **Signal Integrity Toolbox™**

User's Guide

# MATLAB®

## **How to Contact MathWorks**

Latest news: www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

T

Phone: 508-647-7000

The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

Signal Integrity Toolbox™ User's Guide

© COPYRIGHT 2021-2023 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

$MathWorks\ products\ are\ protected\ by\ one\ or\ more\ U.S.\ patents.\ Please\ see\ www.mathworks.com/patents\ for\ more\ information.$

## **Revision History**

| September 2021 | Online only | New for Version 1.0 (Release 2021b)     |

|----------------|-------------|-----------------------------------------|

| March 2022     | Online only | Revised for Version 1.1 (Release 2022a) |

| September 2022 | Online only | Revised for Version 1.2 (Release 2022b) |

| March 2023     | Online only | Revised for Version 1.3 (Release 2023a) |

# Contents

| Coss in Transmission Line Corners  Fermutation Mode Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Case Mode  Cas |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Permutation Mode Case Mode  Case Mode  STAT Mode  Interpreting Waveform, Eye Diagram, and Timing Results  Eye Diagram DRC  Eye Diagram DRC  Timing Results  I-  Simulation Parameters Used in Serial Link Design  Simulation Parameter Definitions  Determining FFT Block Size  Time Domain Start and Stop Parameters  Specify Corner Conditions in Serial Link Design  IC Environment Corners  Etch Corners  Etch Corners  Impact of Corner Settings  Stimulus Patterns in Serial Link Design  2-  User Stimulus Patterns  2-  Using Stimulus Patterns  2-  Using Stimulus Patterns  2-  2-  2-  2-  2-  2-  2-  2-  2-  2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Permutation Mode Case Mode  STAT Mode  Interpreting Waveform, Eye Diagram, and Timing Results  Waveform DRC Iteye Diagram DRC Itiming Results  Items Configure Serial Link  Configure Serial Link  Simulation Parameters Used in Serial Link Design Simulation Parameter Definitions Determining FFT Block Size Time Domain Start and Stop Parameters  Specify Corner Conditions in Serial Link Design IC Environment Corners Etch Corners Impact of Corner Settings  Stimulus Patterns in Serial Link Design User Stimulus Editor 2-Using Stimulus Patterns 2-Using Stimulus Patter |

| Permutation Mode Case Mode  Case Mode  1- Ca |

| STAT Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Interpreting Waveform, Eye Diagram, and Timing Results  Waveform DRC  Eye Diagram DRC  Timing Results  Configure Serial Ling  Simulation Parameters Used in Serial Link Design  Simulation Parameter Definitions  Determining FFT Block Size  Time Domain Start and Stop Parameters  Specify Corner Conditions in Serial Link Design  IC Environment Corners  Etch Corners  Impact of Corner Settings  Stimulus Patterns in Serial Link Design  User Stimulus Patterns  2 Using Stimulus Patterns  2 Using Stimulus Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Waveform DRC 1. Eye Diagram DRC 1. Timing Results 1.  Configure Serial Link  Configure Seri |

| Waveform DRC 1. Eye Diagram DRC 1. Timing Results 1.  Configure Serial Link  Configure Seri |

| Configure Serial Li  Simulation Parameters Used in Serial Link Design Simulation Parameter Definitions Determining FFT Block Size Time Domain Start and Stop Parameters  Specify Corner Conditions in Serial Link Design IC Environment Corners Etch Corners Impact of Corner Settings  Stimulus Patterns in Serial Link Design User Stimulus Editor 2 Using Stimulus Patterns 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Configure Serial Li  Simulation Parameters Used in Serial Link Design Simulation Parameter Definitions Determining FFT Block Size Time Domain Start and Stop Parameters  Specify Corner Conditions in Serial Link Design IC Environment Corners Etch Corners Impact of Corner Settings  Stimulus Patterns in Serial Link Design User Stimulus Editor 2 Using Stimulus Patterns 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

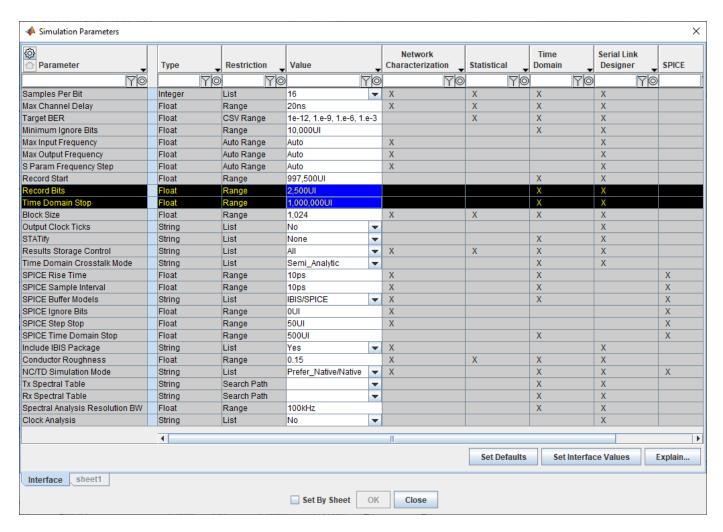

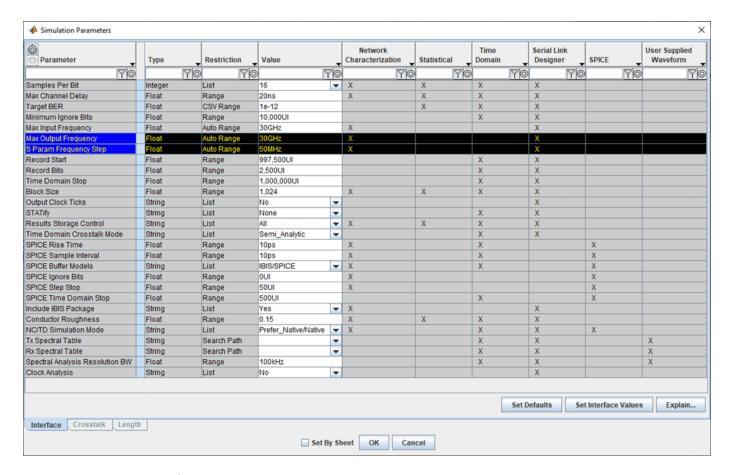

| Simulation Parameters Used in Serial Link Design Simulation Parameter Definitions Determining FFT Block Size Time Domain Start and Stop Parameters  Specify Corner Conditions in Serial Link Design IC Environment Corners Etch Corners Impact of Corner Settings  Stimulus Patterns in Serial Link Design User Stimulus Editor Using Stimulus Patterns  2 Using Stimulus Patterns 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Simulation Parameters Used in Serial Link Design Simulation Parameter Definitions Determining FFT Block Size Time Domain Start and Stop Parameters  Specify Corner Conditions in Serial Link Design IC Environment Corners Etch Corners Impact of Corner Settings  Stimulus Patterns in Serial Link Design User Stimulus Editor Using Stimulus Patterns  2 Using Stimulus Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

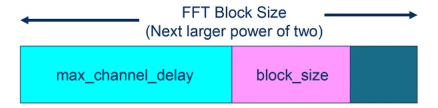

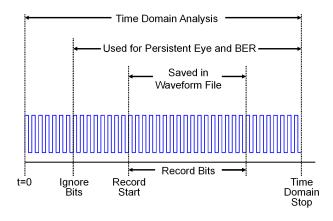

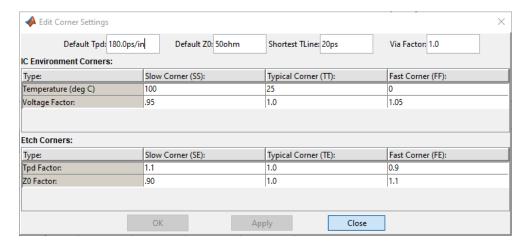

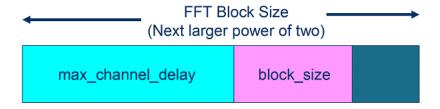

| Simulation Parameter Definitions Determining FFT Block Size Time Domain Start and Stop Parameters  Specify Corner Conditions in Serial Link Design IC Environment Corners Etch Corners Impact of Corner Settings  Stimulus Patterns in Serial Link Design User Stimulus Editor Using Stimulus Patterns  2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

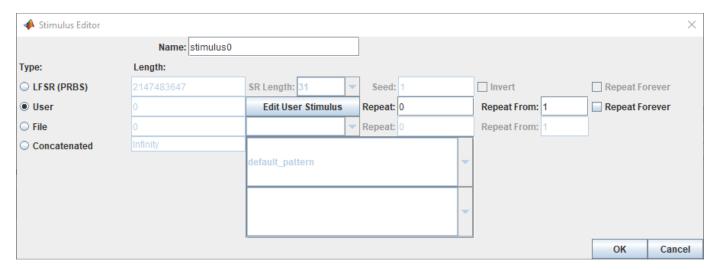

| User Stimulus Editor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| User Stimulus Editor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Using Stimulus Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pre-Layout Analysis of Serial Li                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Pre-Layout Analysis of Serial Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

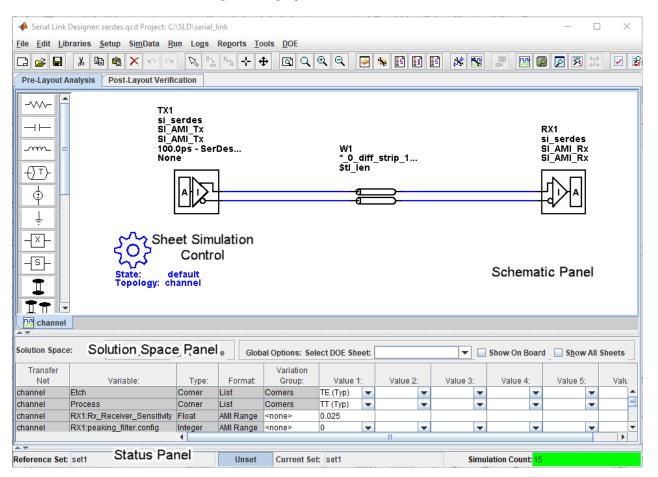

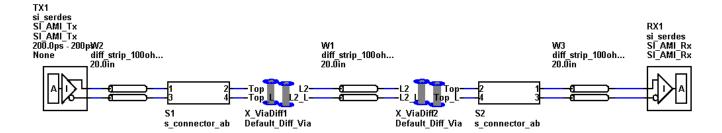

| Schematic Elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          | Customize Serial Link Project for Pre-Layout Analysis | 3-5<br>3-5 |

|----------|-------------------------------------------------------|------------|

|          | Using I/O buffers                                     | 3-5<br>3-5 |

|          | Using Transmission Lines                              | 3-5<br>3-6 |

|          | Using S-Parameters                                    | 3-6        |

|          | Osing 5-1 drameters                                   | 3-0        |

|          | Results of Pre-Layout Analysis in Serial Link         | 3-7        |

|          | Validation Reports                                    | 3-7        |

|          | Netlist Generation Report                             | 3-7        |

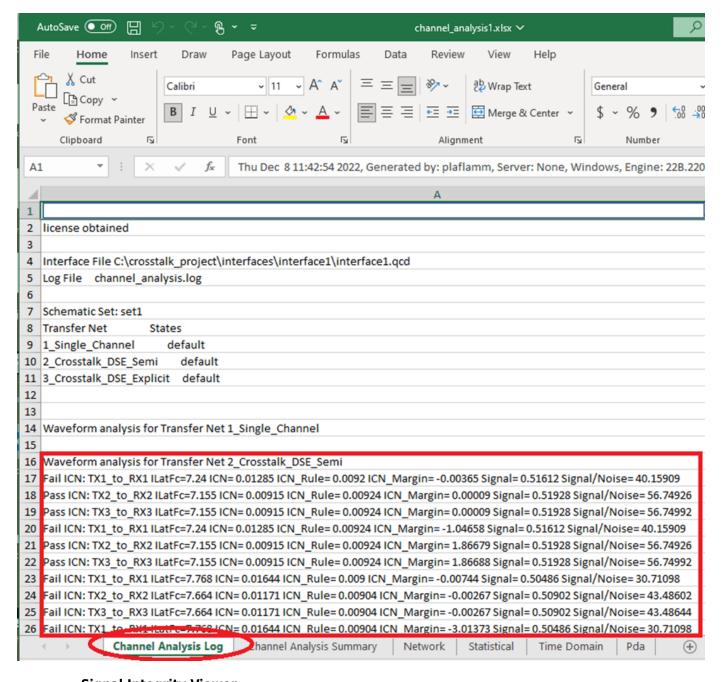

|          | Channel Analysis Report                               | 3-8        |

|          |                                                       |            |

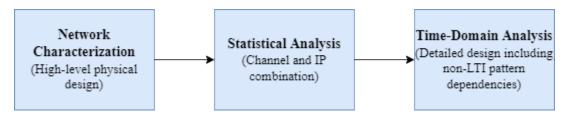

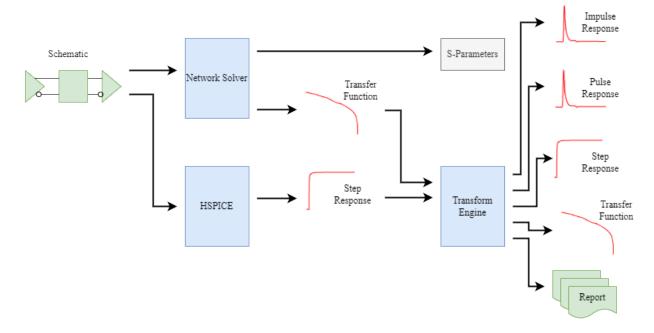

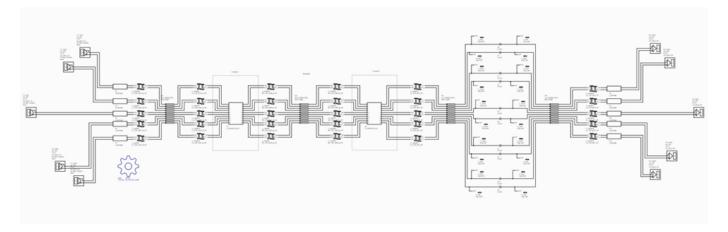

|          | Analysis Flow in Serial Link Design                   | 3-9        |

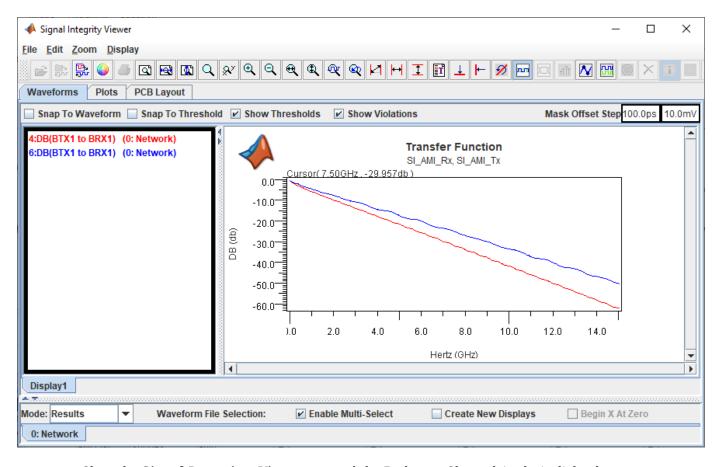

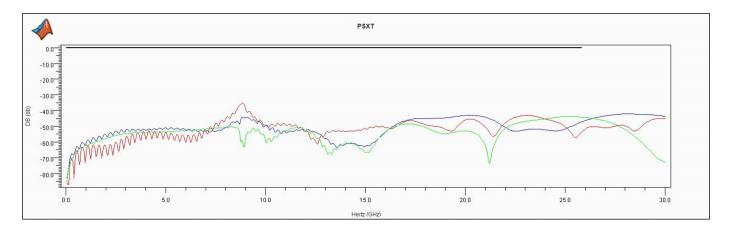

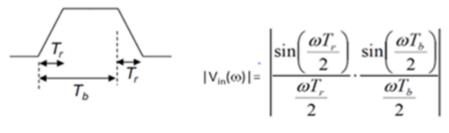

|          | Network Characterization                              | 3-9        |

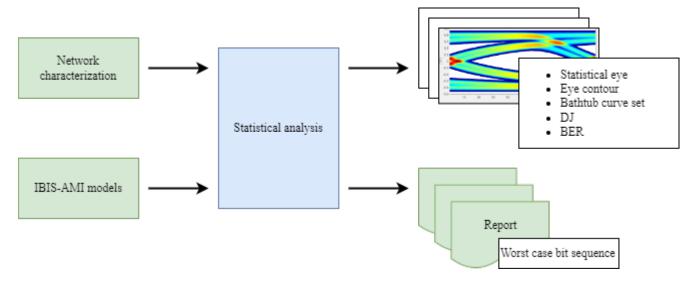

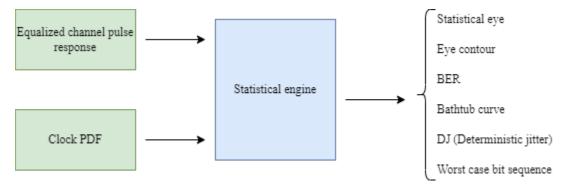

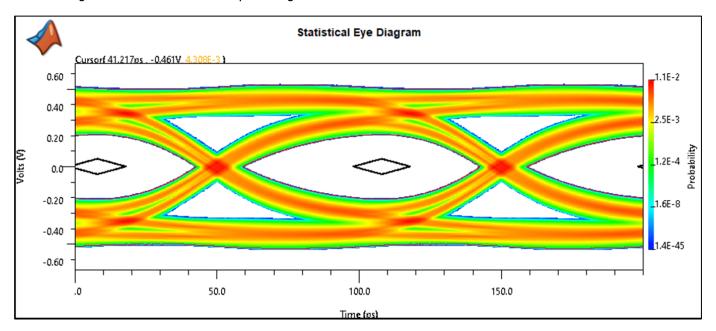

|          | Statistical Analysis                                  | 3-11       |

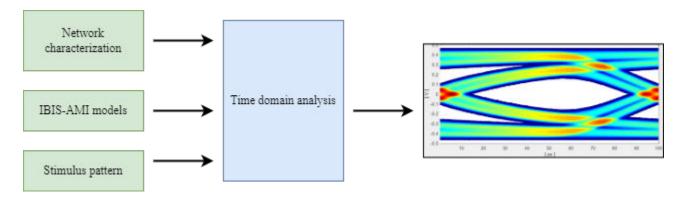

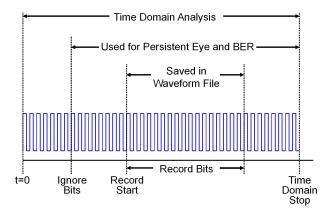

|          | Time-Domain Analysis                                  | 3-13       |

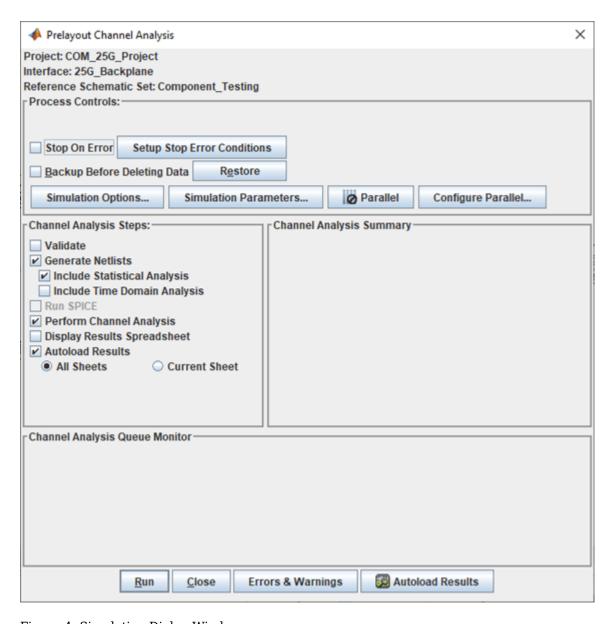

|          | Pre-Layout Analysis                                   | 3-15       |

|          | Post-Layout Analysis                                  | 3-16       |

|          |                                                       |            |

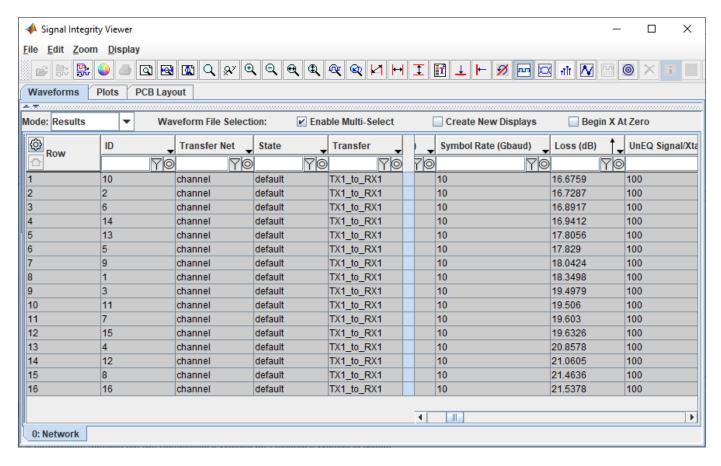

|          | Network Characterization Results                      | 3-17       |

|          | Results to View                                       | 3-17       |

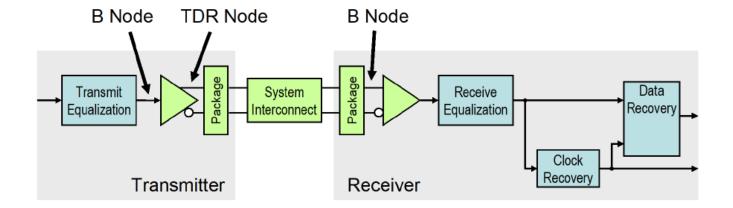

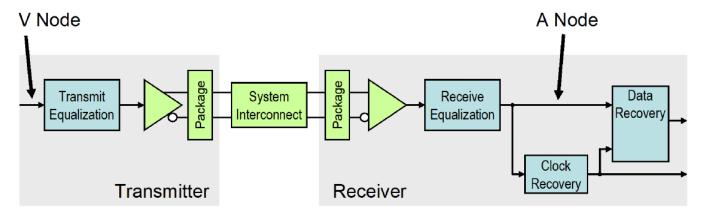

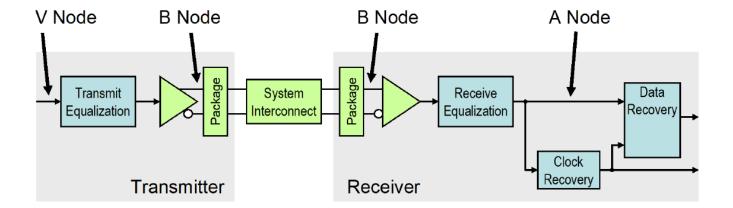

|          | Node Locations                                        | 3-18       |

|          | Table Column Definitions                              | 3-19       |

|          |                                                       | 2 22       |

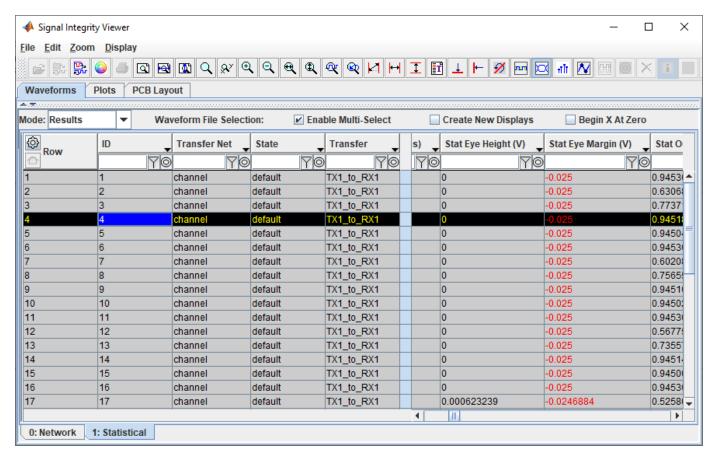

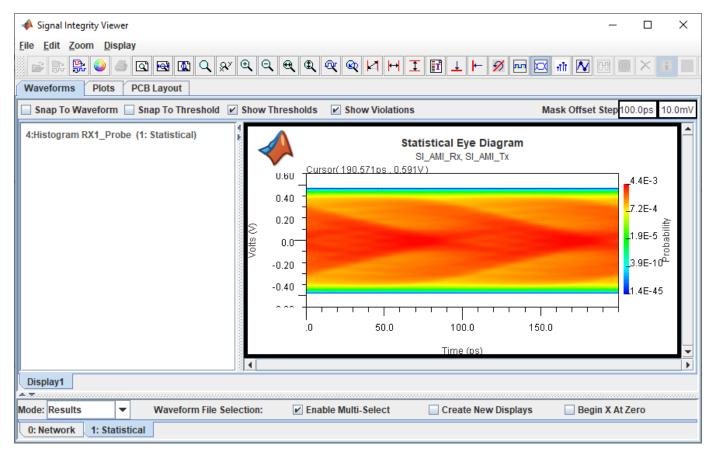

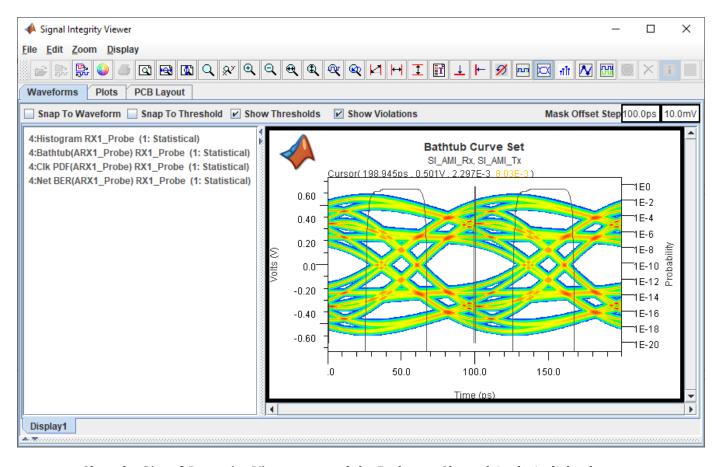

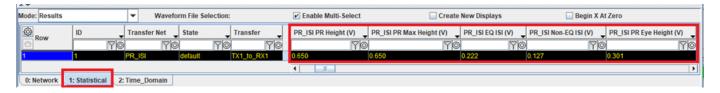

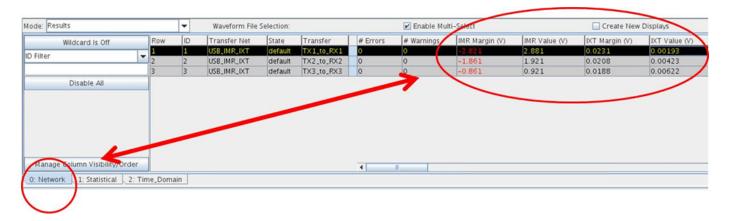

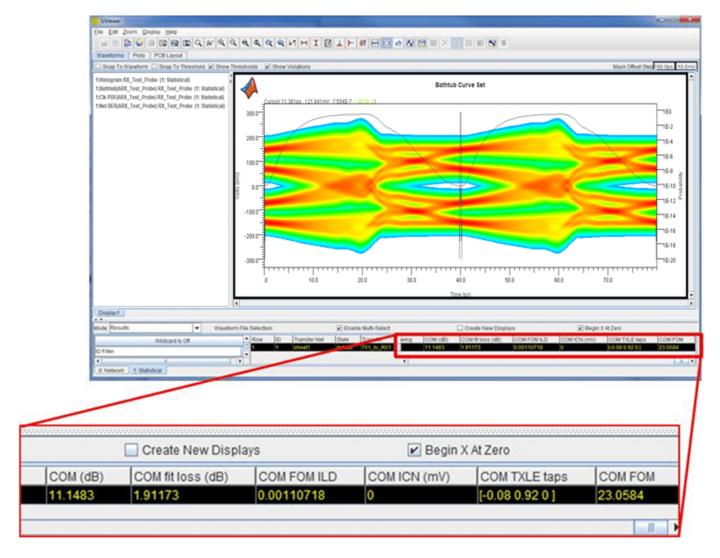

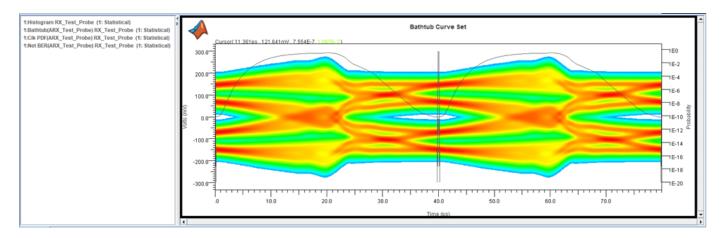

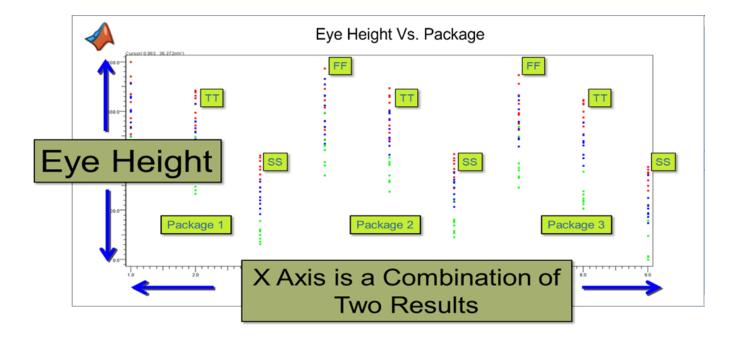

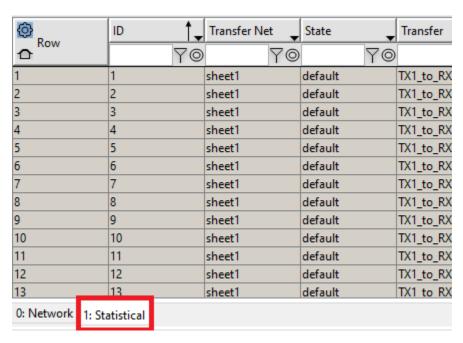

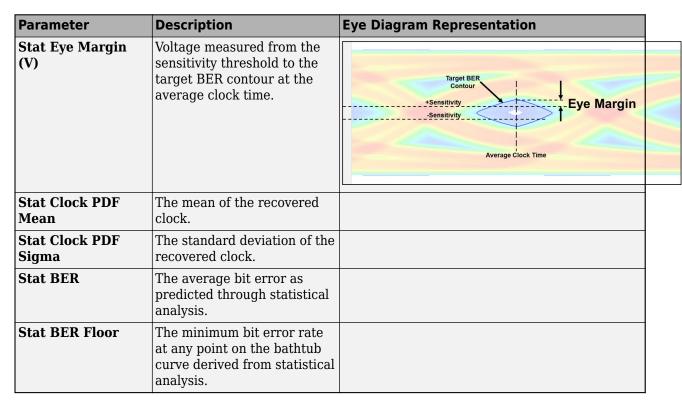

|          | Statistical Analysis Results                          | 3-22       |

|          | Results to View                                       | 3-22       |

|          | Node Locations                                        | 3-23       |

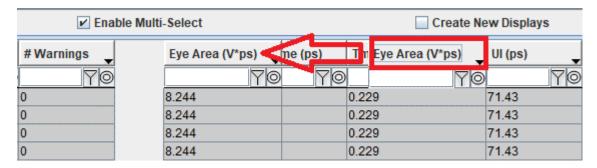

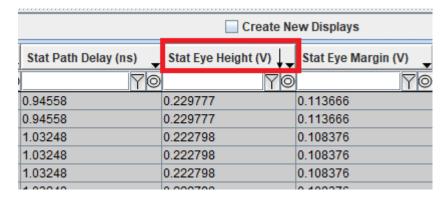

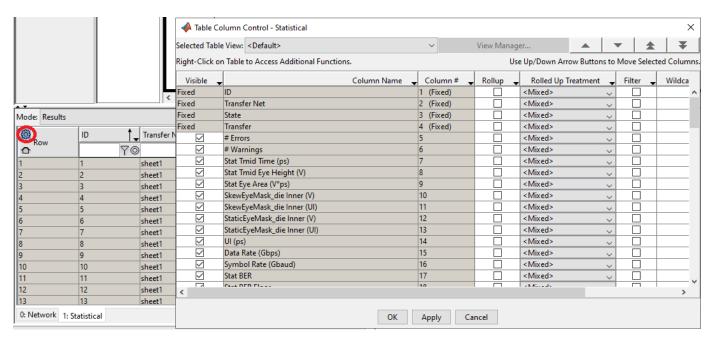

|          | Table Column Definitions                              | 3-23       |

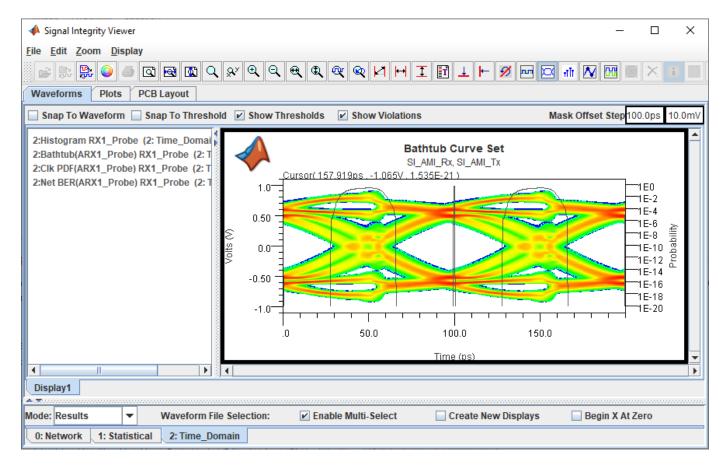

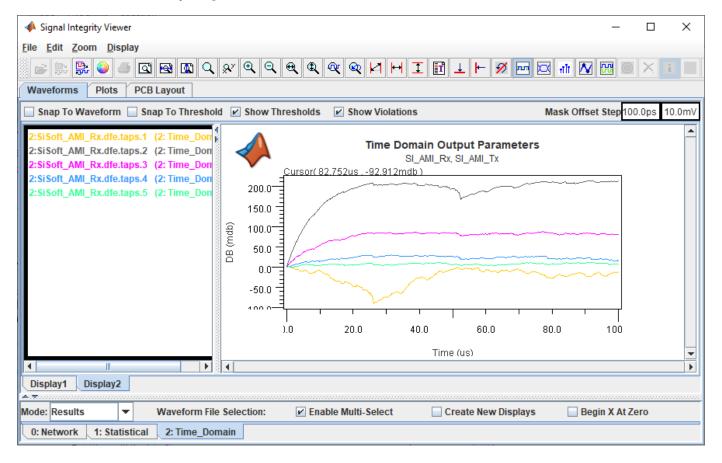

|          | Time Domain Analysis Results                          | 3-26       |

|          | Results to View                                       | 3-26       |

|          | Node Locations                                        | 3-26       |

|          | Table Column Definitions                              | 3-20       |

|          | Tubic Column Definitions                              | 32,        |

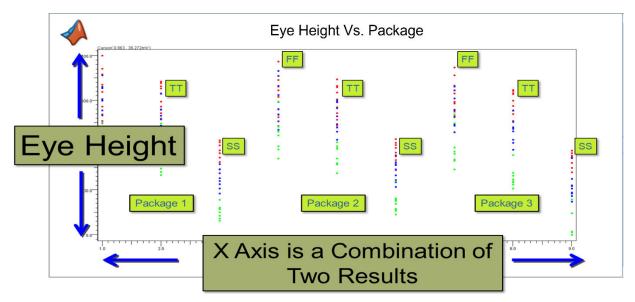

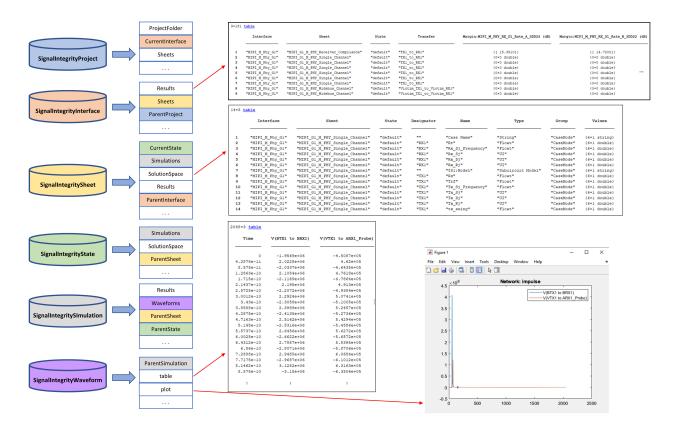

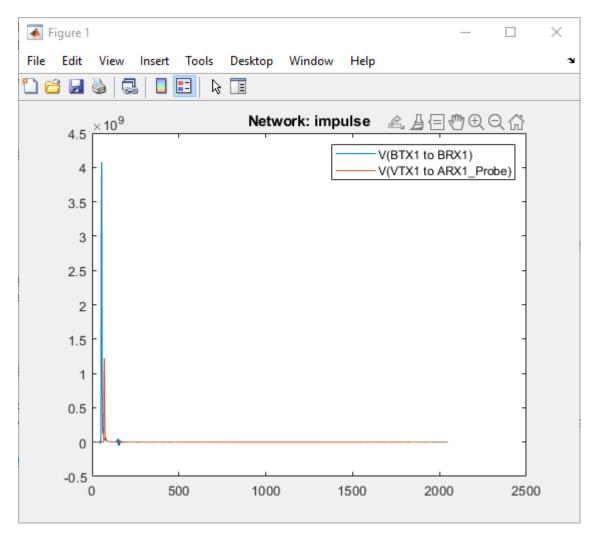

|          | Managing Simulation Data and Results                  | 3-29       |

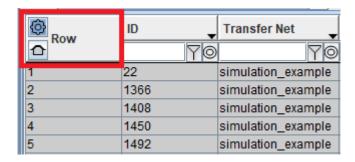

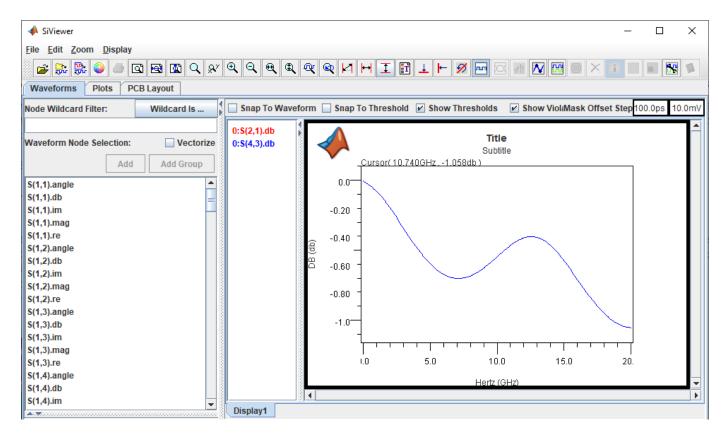

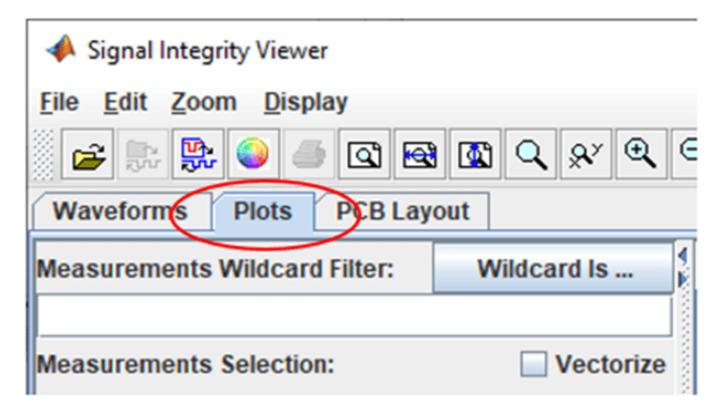

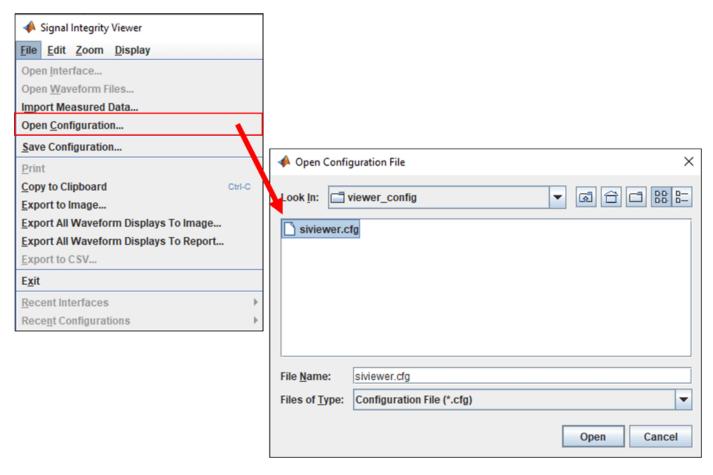

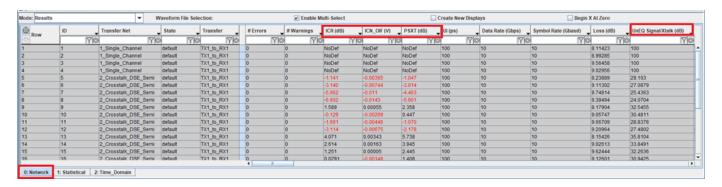

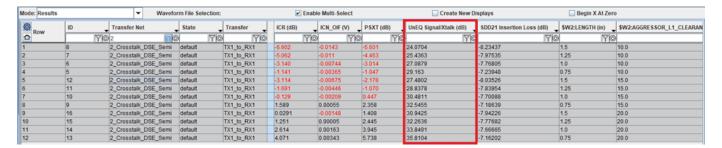

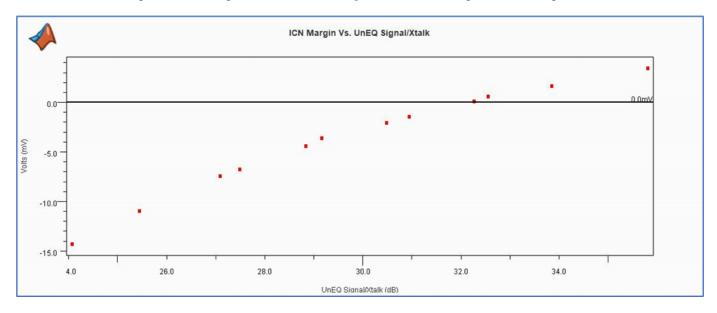

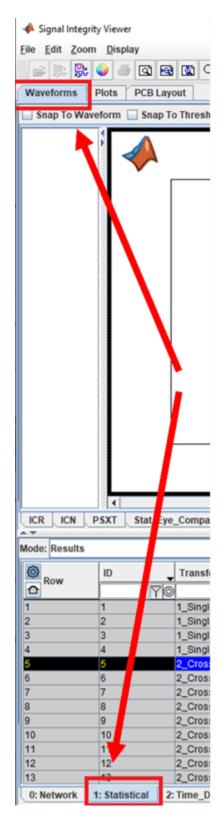

|          | Data Mining from Signal Integrity Viewer App Window   | 3-29       |

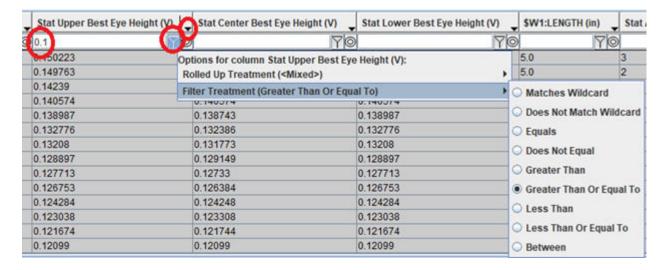

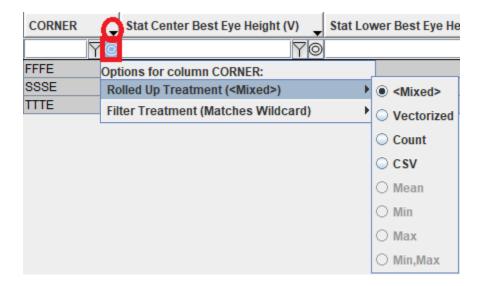

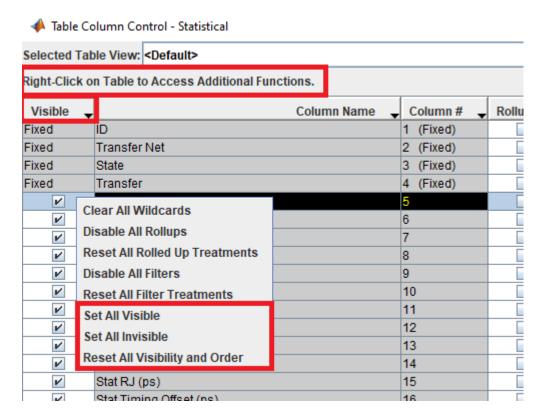

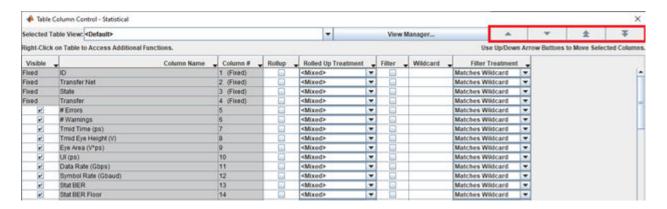

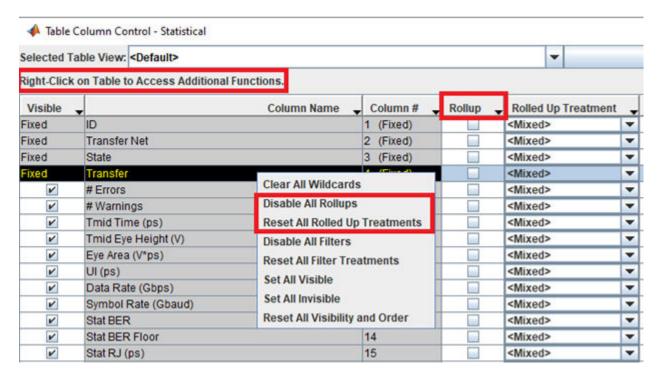

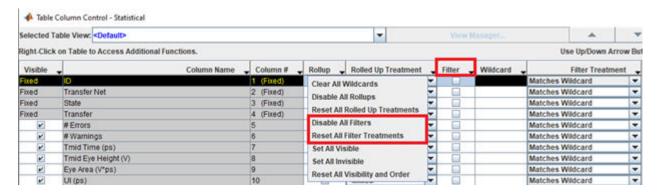

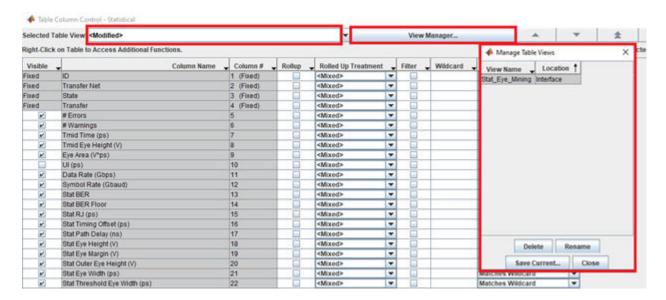

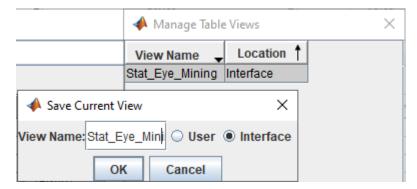

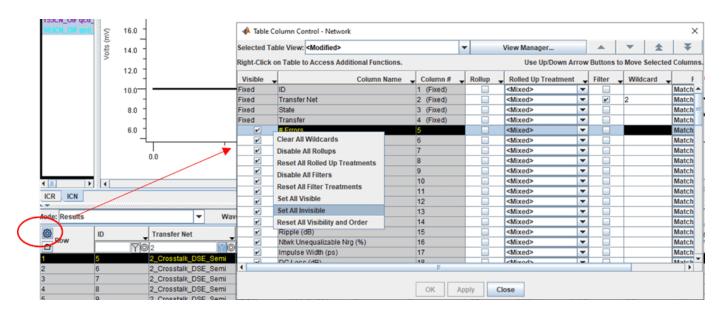

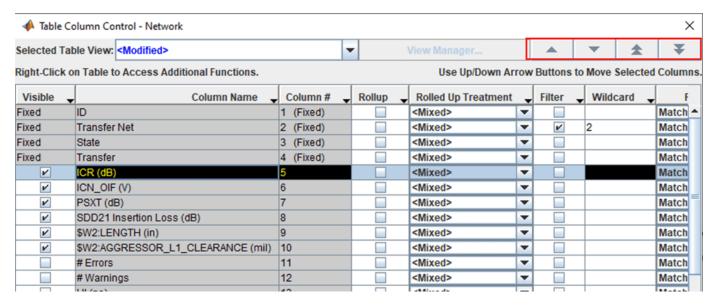

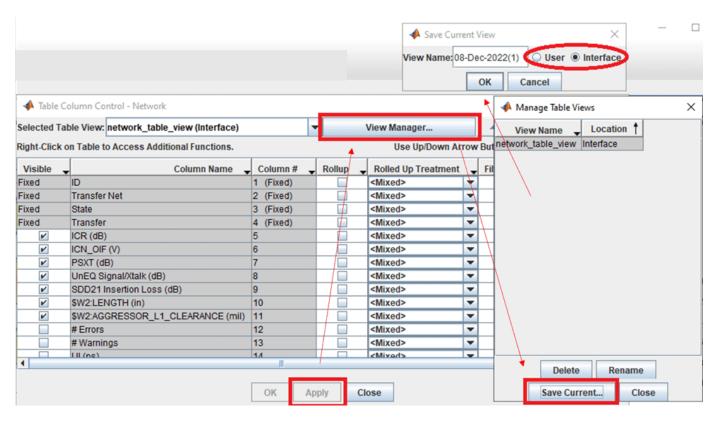

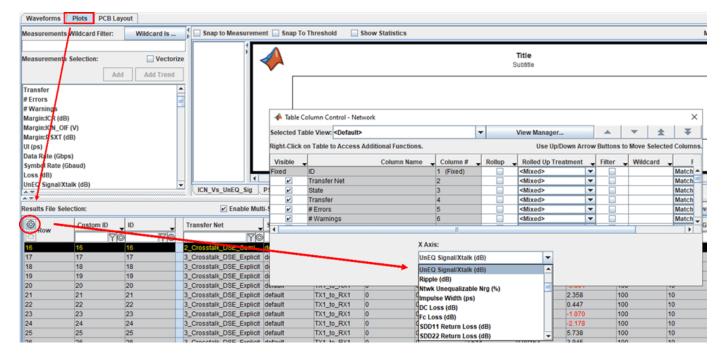

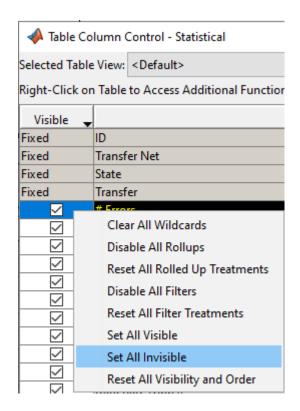

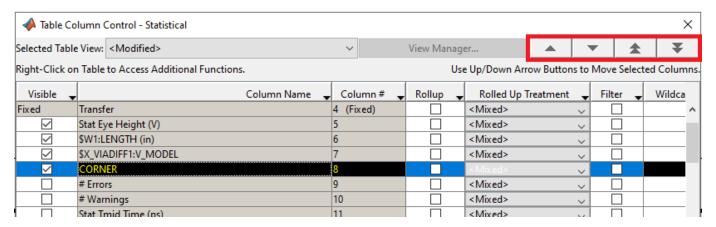

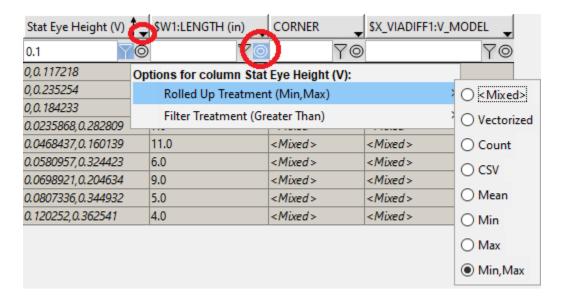

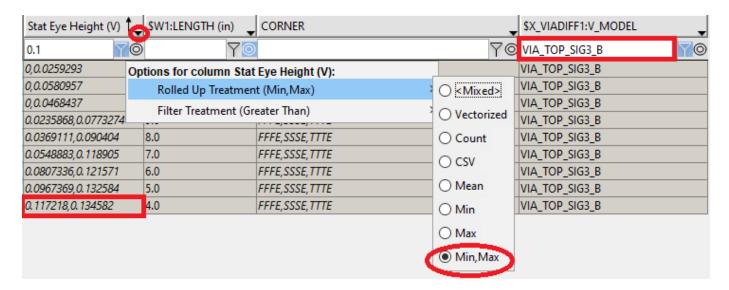

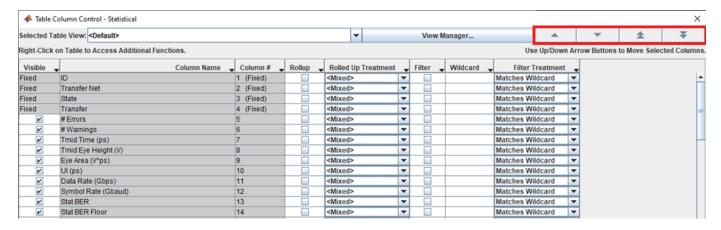

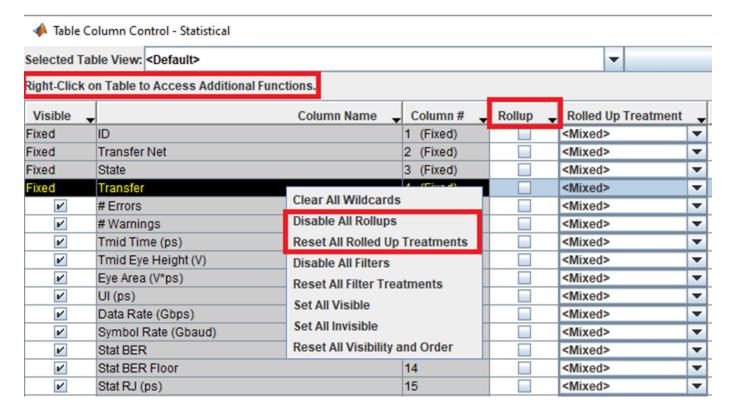

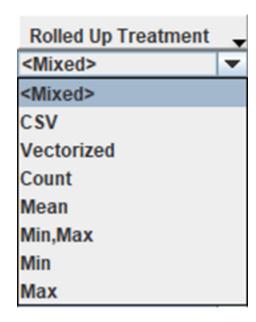

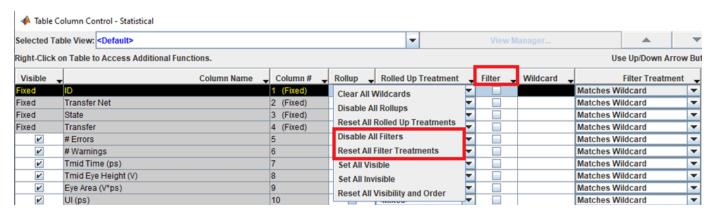

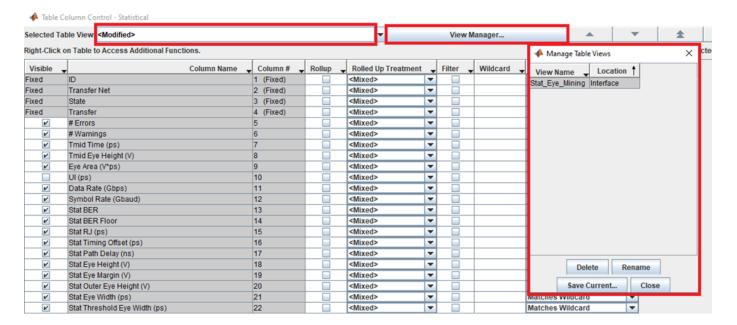

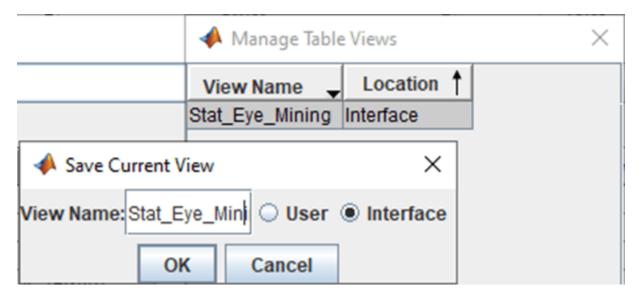

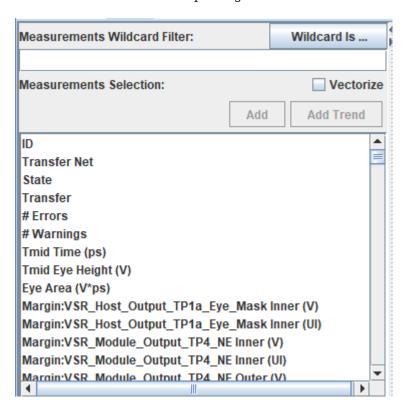

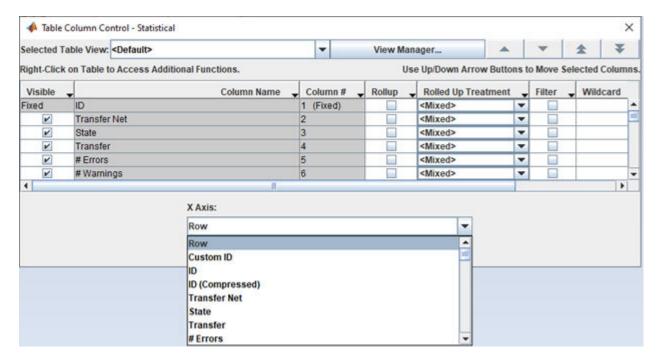

|          | Data Mining Using Table Column Control                | 3-31       |

|          |                                                       |            |

| 1 [      | Post-Layout Verification of Serial                    | Link       |

| <b>T</b> |                                                       |            |

|          | Post-Layout Verification of Serial Link               | 4-2        |

|          | Board                                                 | 4-3        |

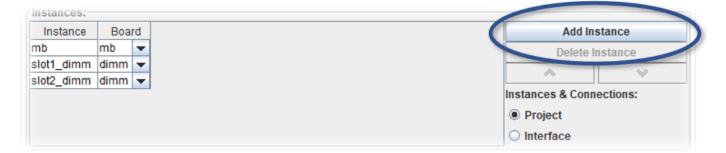

|          | Instance                                              | 4-3        |

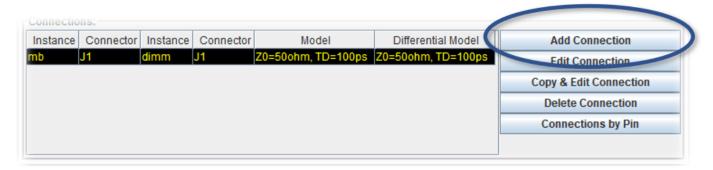

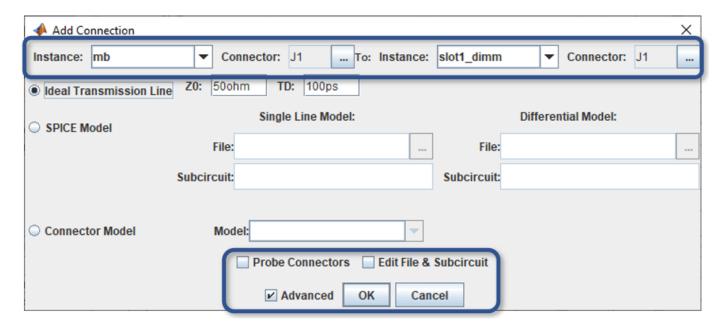

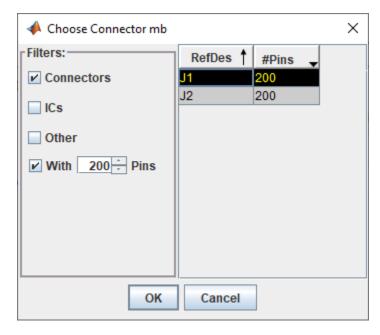

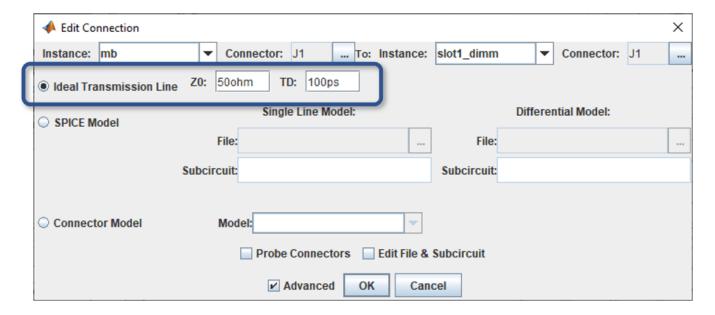

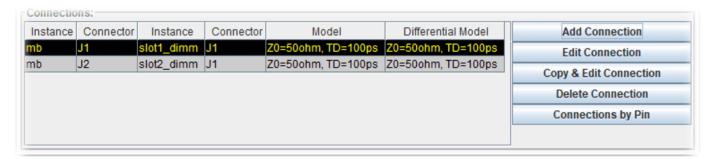

|          | Connection                                            | 4-4        |

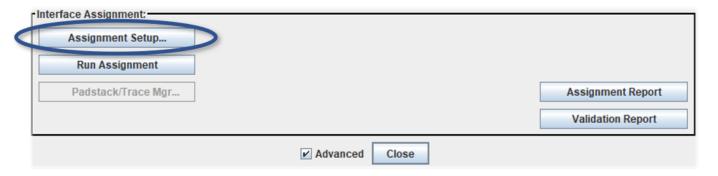

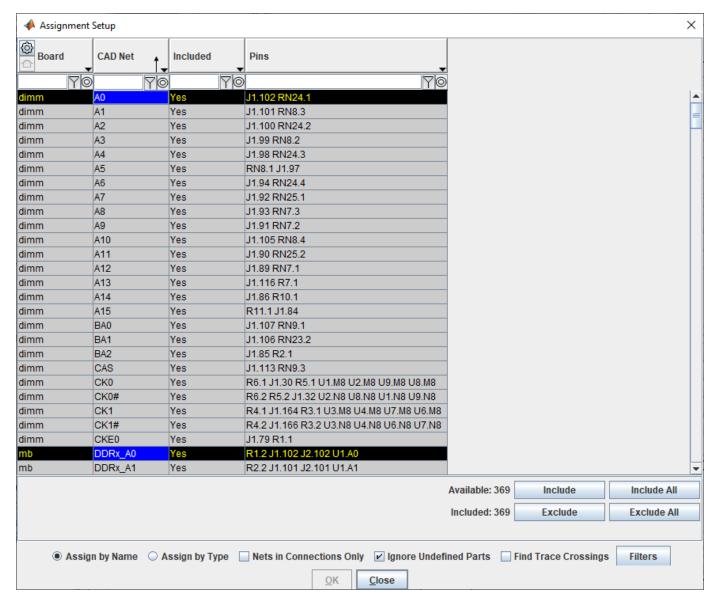

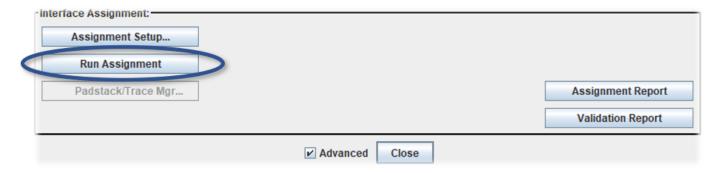

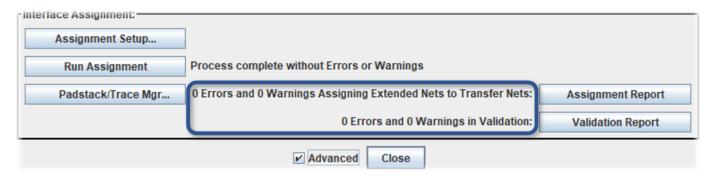

|          | Assignment                                            | 4-4        |

|          | Population                                            | 4-5        |

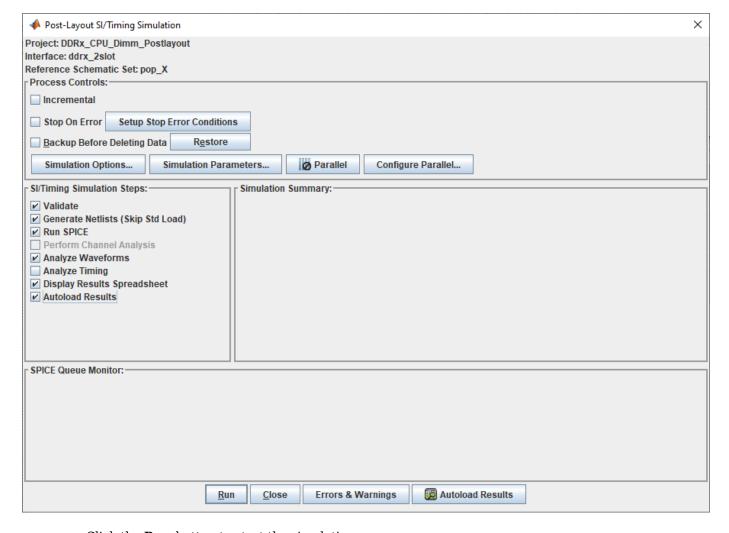

|          | Simulation                                            | 4-5        |

|          | Topology                                              | 4-5        |

|          |                                                       |            |

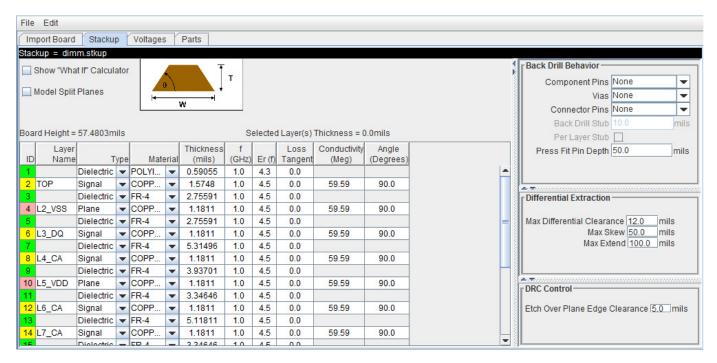

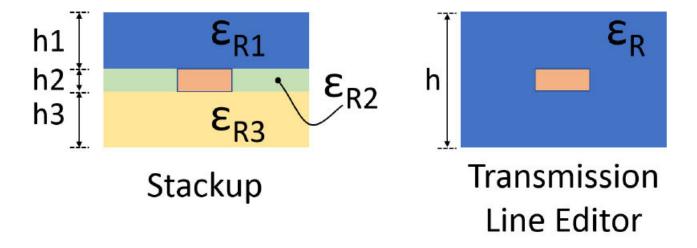

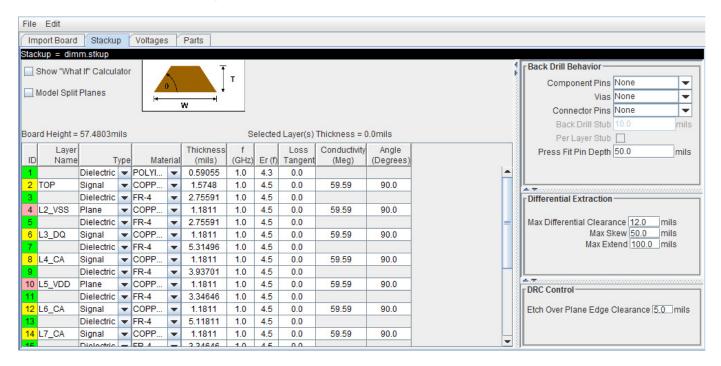

|          | Stackup and Extraction Control in Serial Link Project | 4-6        |

|          | Stackup Editor                                        | 4-6        |

|          | Extraction Control                                    | <b>4-7</b> |

|          |                                                       |            |

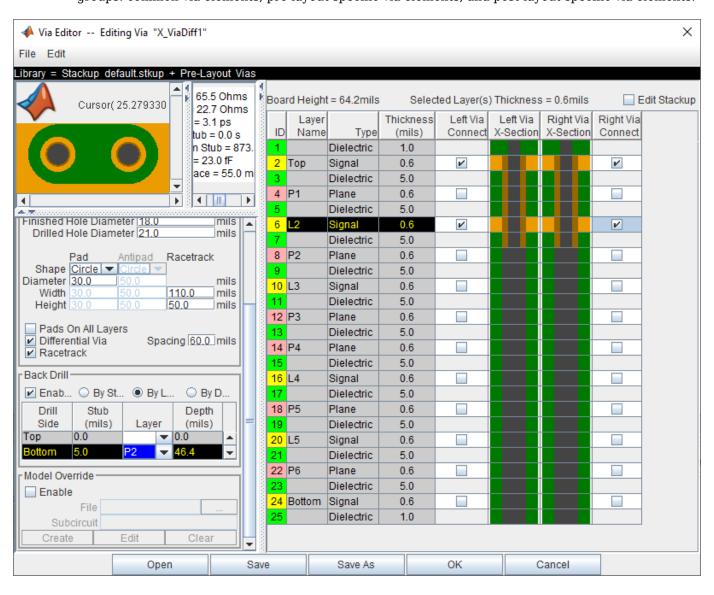

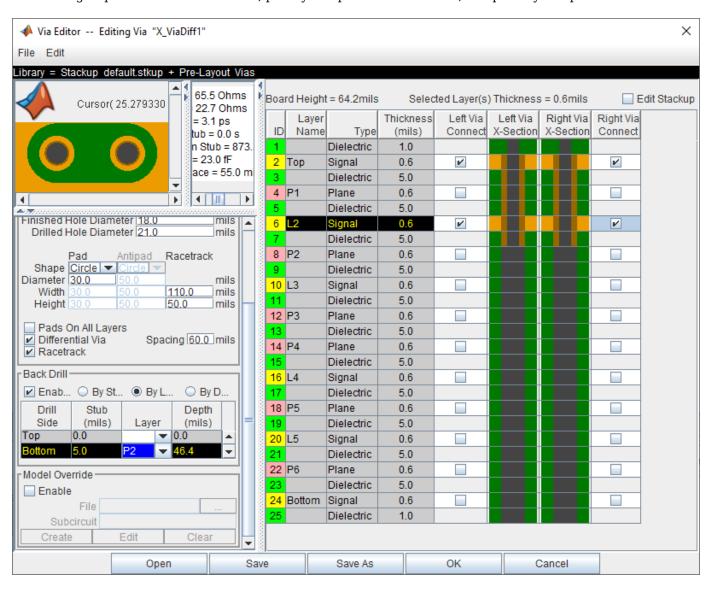

|            | Via and Stackup Management in Serial Link Project  | 4-9          |

|------------|----------------------------------------------------|--------------|

|            | Via Elements                                       | 4-10<br>4-10 |

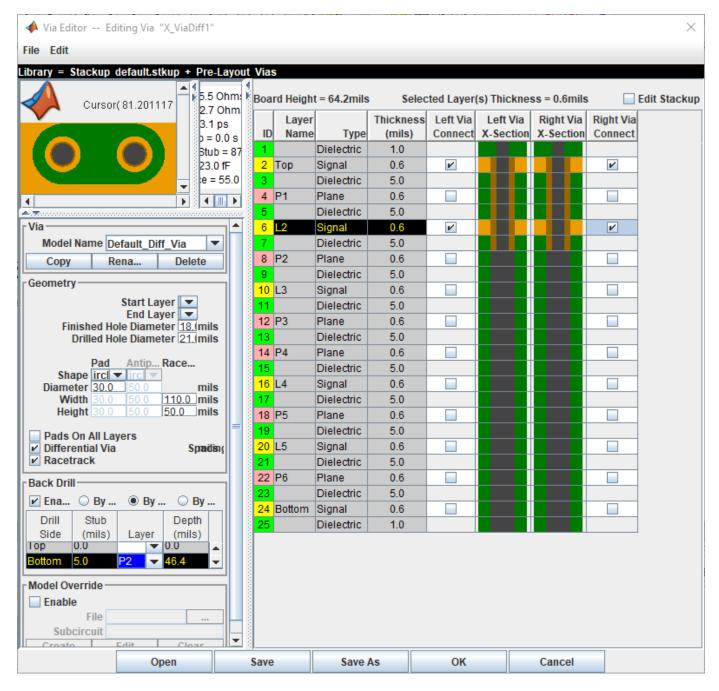

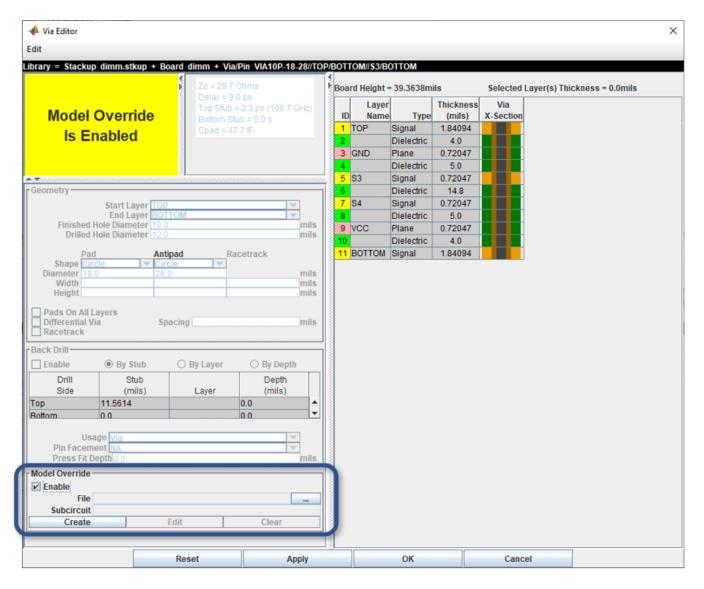

|            | Editing Via for Post-Layout Simulations            | 4-10<br>4-11 |

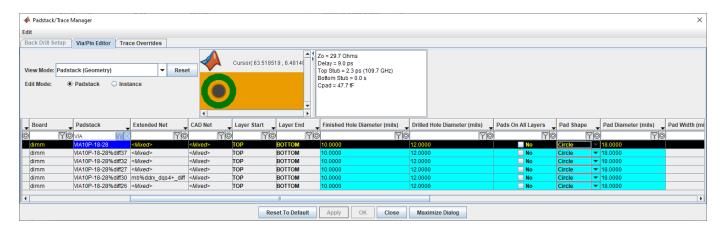

|            | Padstack Definitions                               | 4-11<br>4-11 |

|            | Padstack Editor View Modes                         | 4-11         |

|            | Padstack Editor Edit Modes                         | 4-12         |

|            | Common Operations                                  | 4-12         |

|            | Trace Overrides Tab                                | 4-13         |

|            | Post-Layout to Pre-Layout Extraction               | 4-15<br>4-15 |

| <b>5</b> [ | Serial Link Featured Exan                          | nples        |

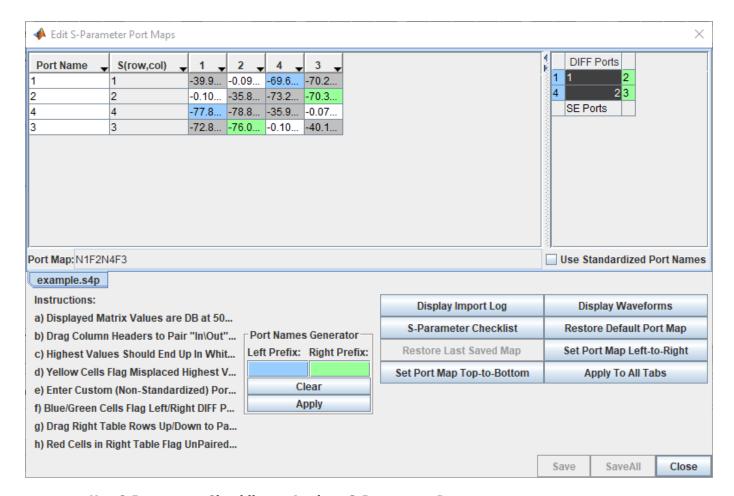

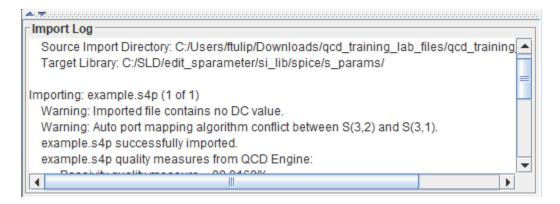

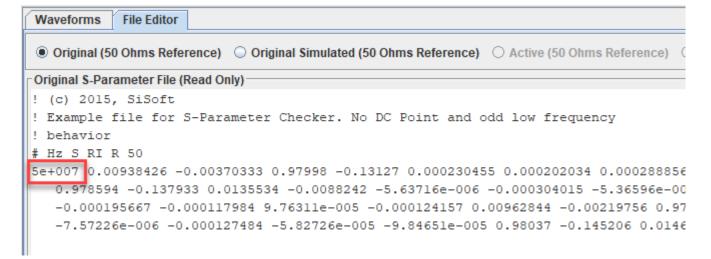

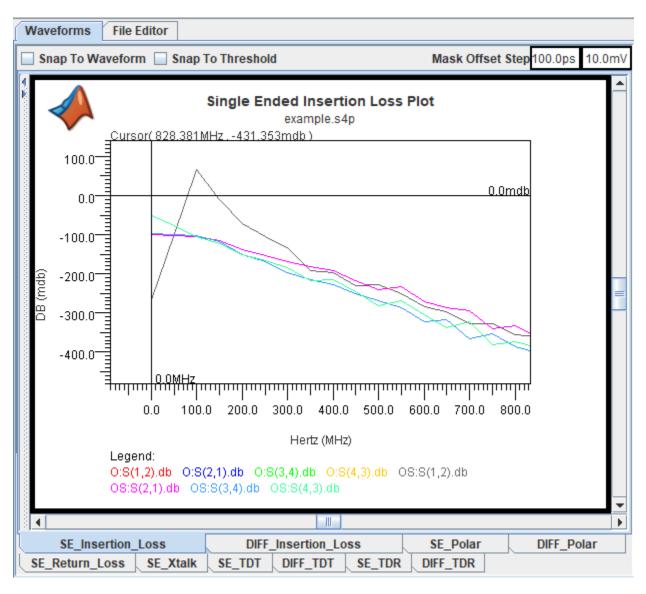

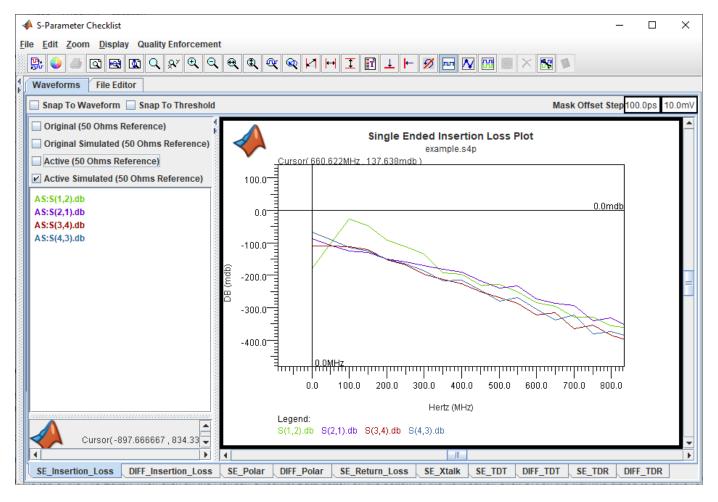

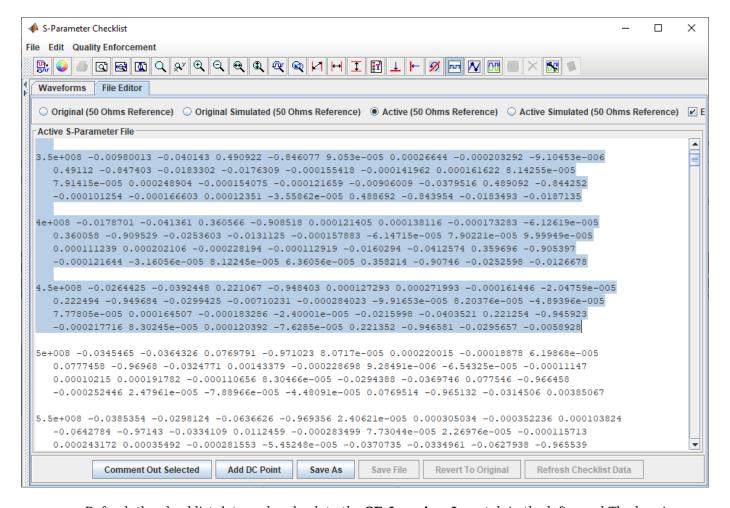

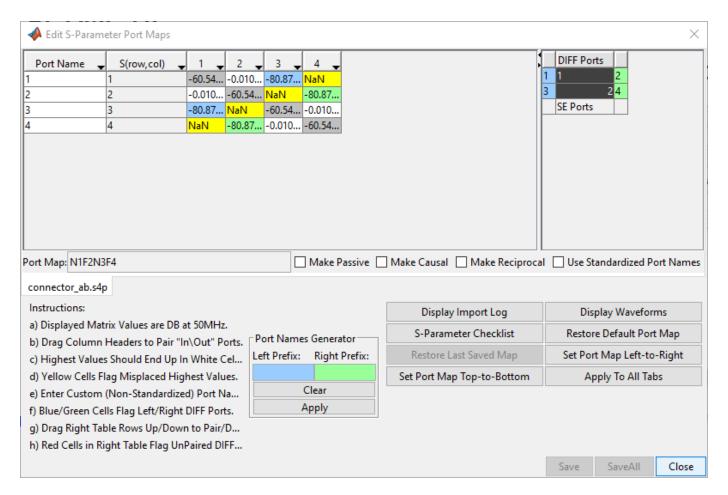

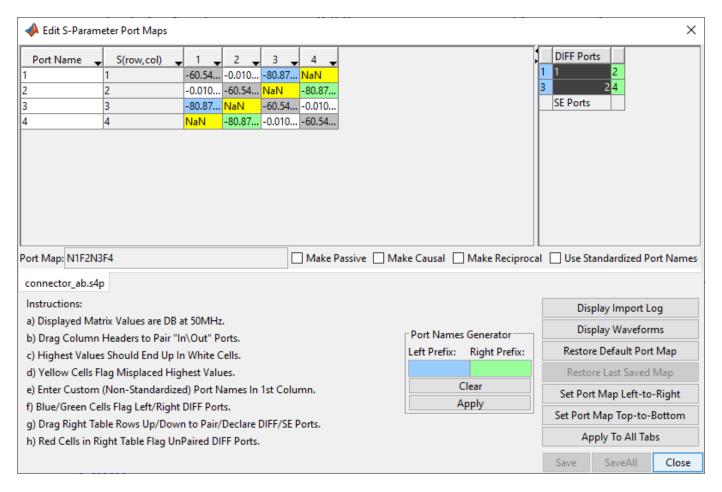

| l          | Edit Imported S-Parameter Data                     | 5-2          |

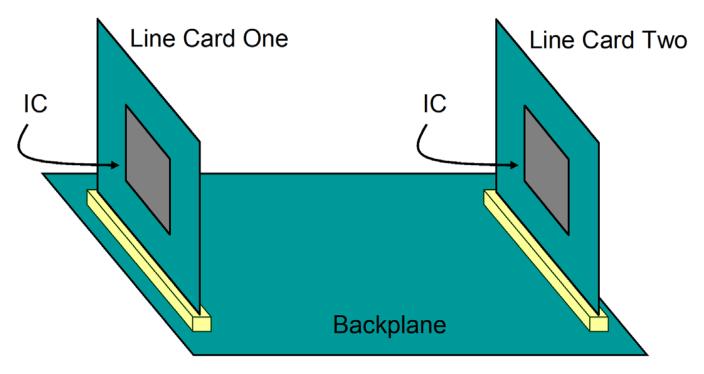

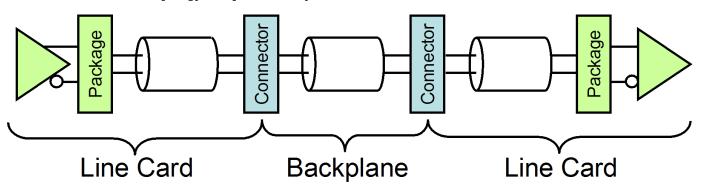

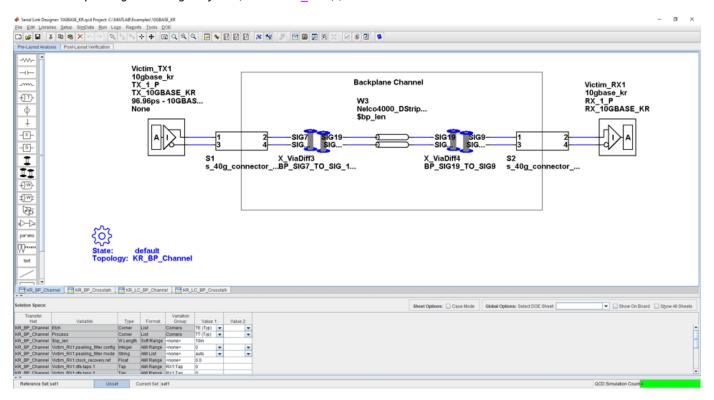

|            | Analyze Backplane with Line Cards                  | 5-10         |

|            | Creating Compliance Masks in Serial Link Designer  | 5-28         |

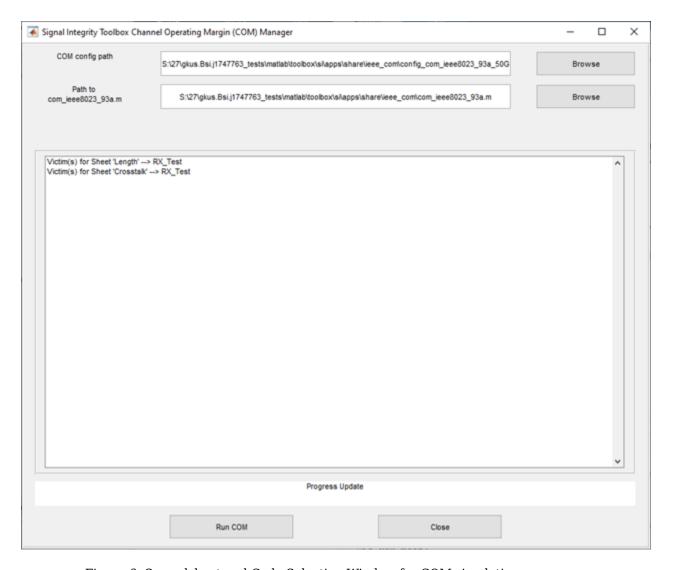

|            | Channel Operating Margin (COM) for Serial Link     | 5-57         |

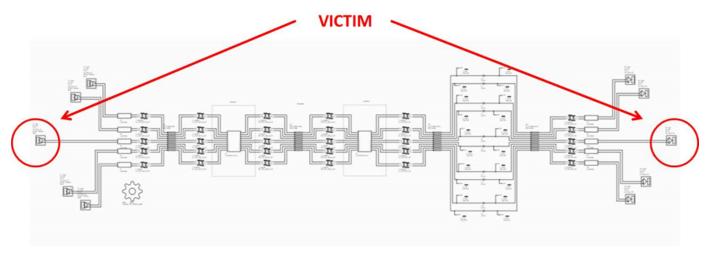

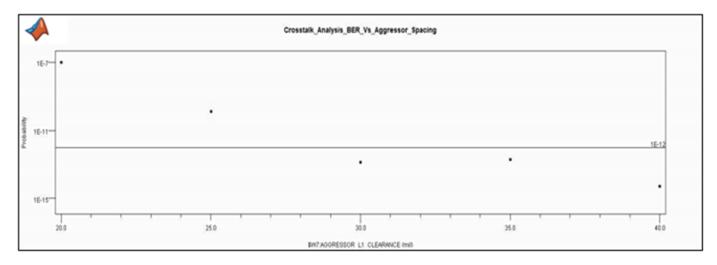

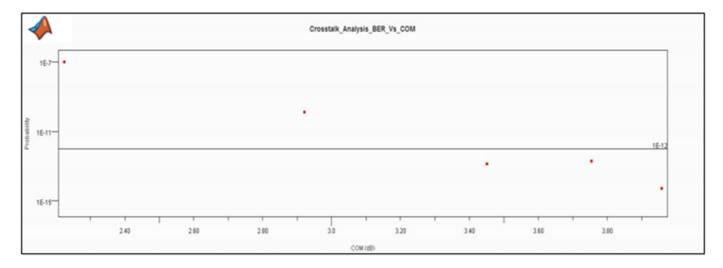

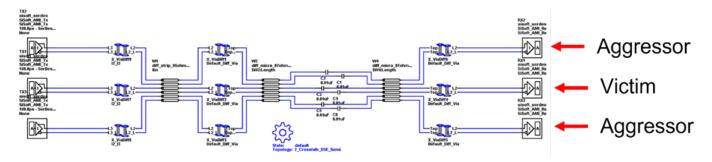

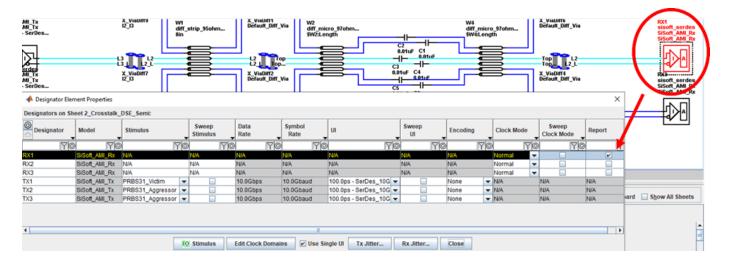

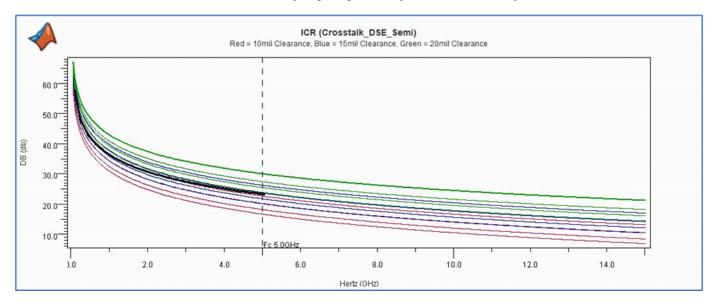

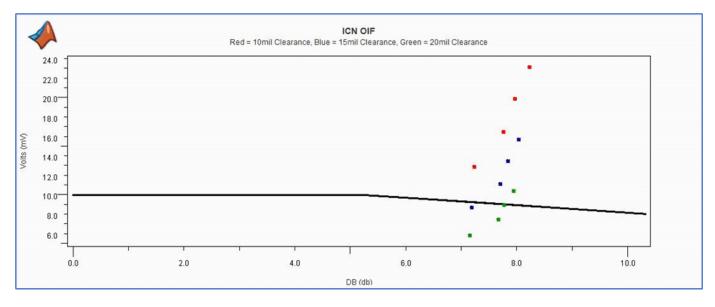

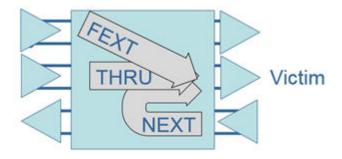

|            | Crosstalk Analysis with Serial Link Designer       | 5-71         |

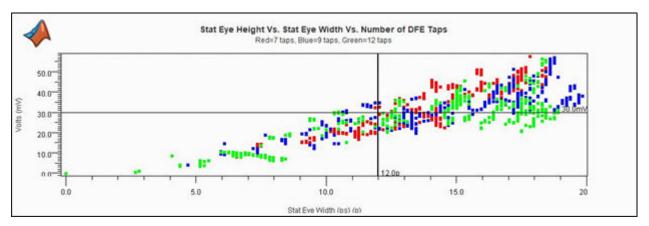

|            | Advanced Visualization with Serial Link Designer   | 5-95         |

|            | Data Mining With Signal Integrity Viewer           | 5-101        |

|            | Configure Parallel                                 | Link         |

| 6          |                                                    |              |

|            | Simulation Parameters Used in Parallel Link Design |              |

|            | Non-STAT Mode SPICE Simulation                     | 6-2          |

|            | STAT Mode SPICE Simulation                         |              |

|            | Waveform Analysis Parameters                       |              |

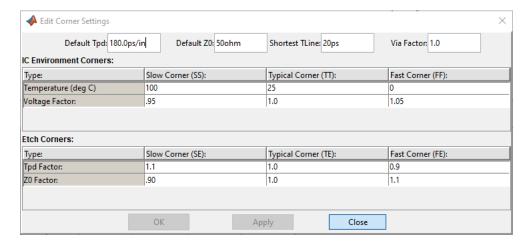

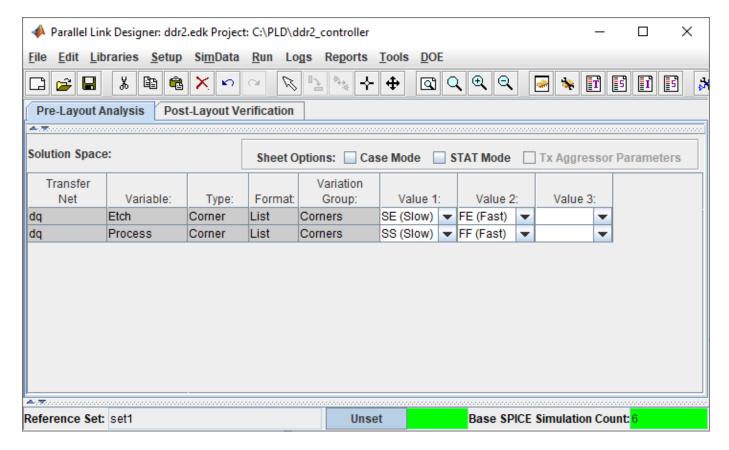

|            | Specify Corner Conditions in Parallel Link Design  | 6-6          |

|            | IC Environment Corners                             | 6-6          |

|            | Etch Corners                                       | 6-6          |

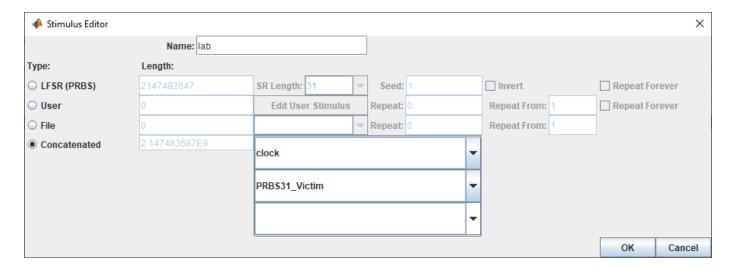

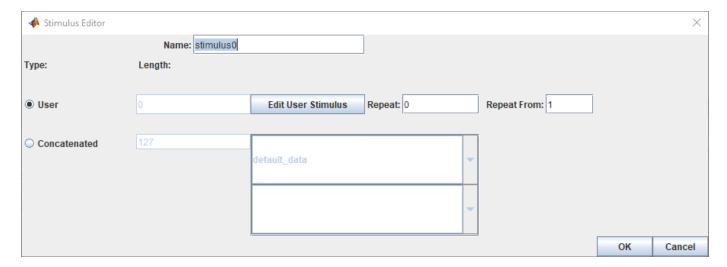

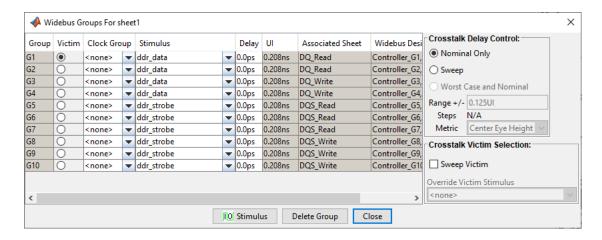

|            | Stimulus Patterns in Parallel Link Design          | 6-9          |

|            | Editing Stimulus Patterns                          | 6-9          |

|            | User Stimulus Editor                               | 6-10<br>6-10 |

|            | Using Stimulus Pattern                             | 6-11         |

| <b>.</b>   |          | C D     |     |      |

|------------|----------|---------|-----|------|

| Pre-Lavout | Analysis | ot Para | Hel | Link |

| • |

|---|

|   |

|   |

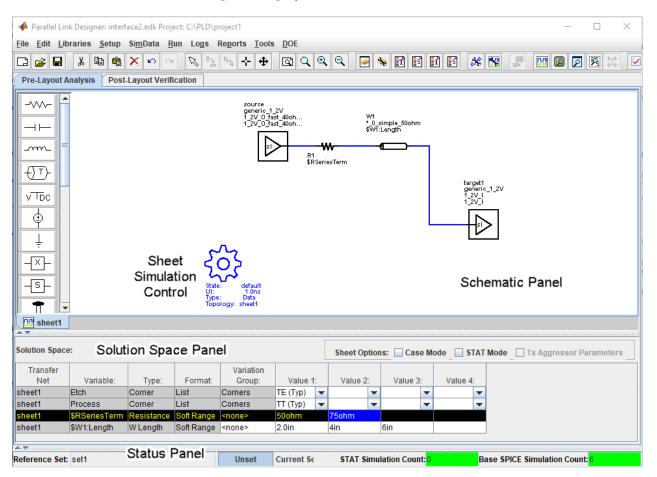

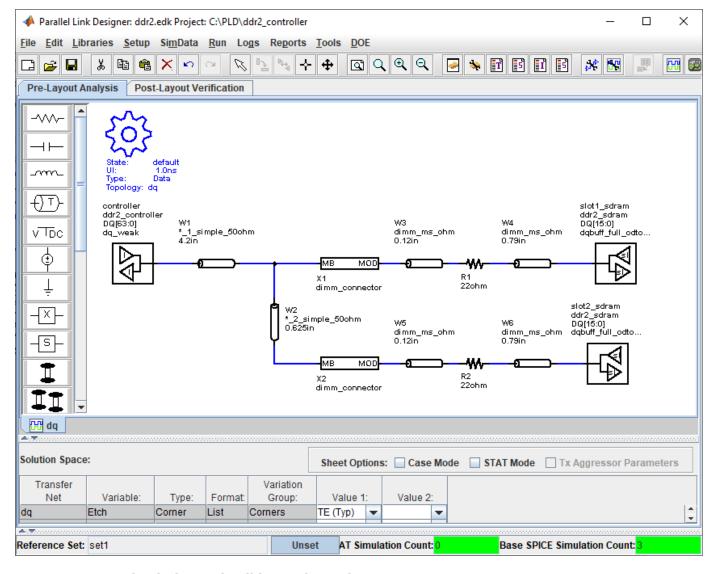

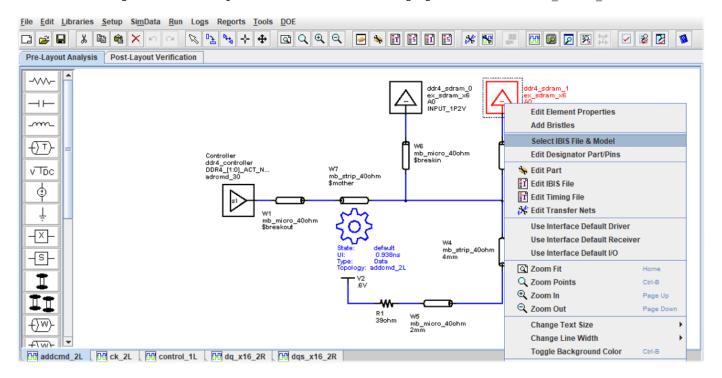

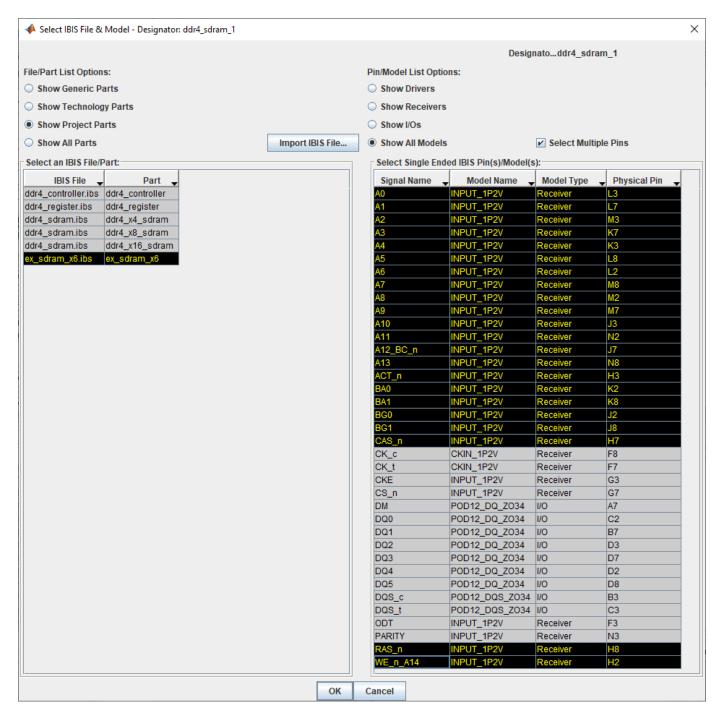

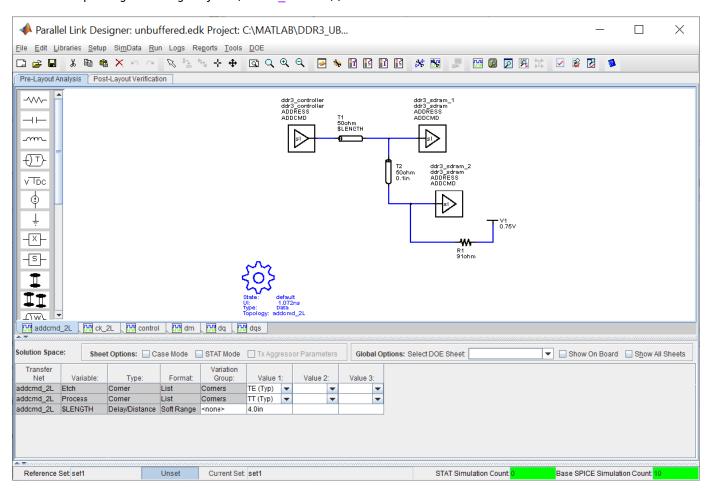

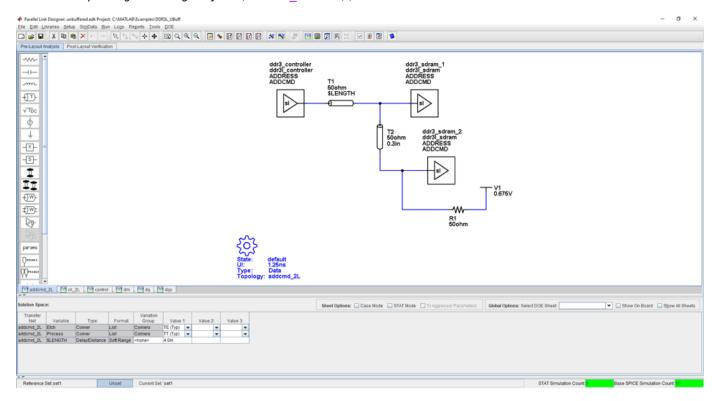

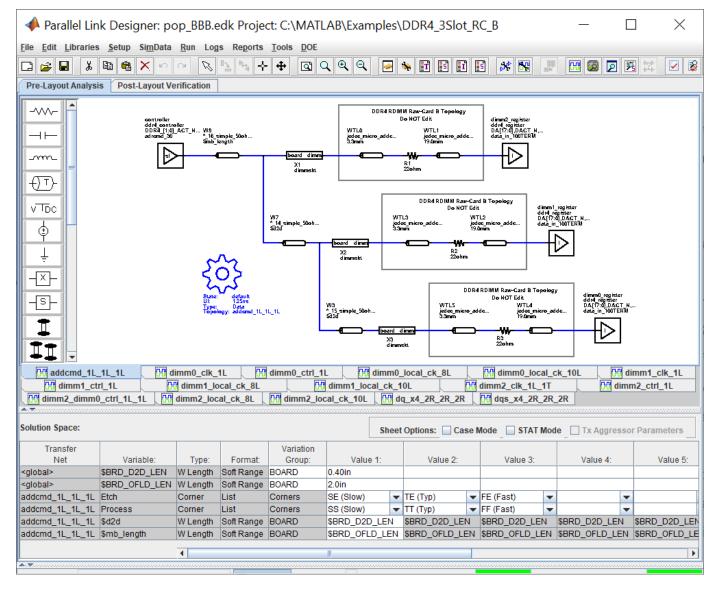

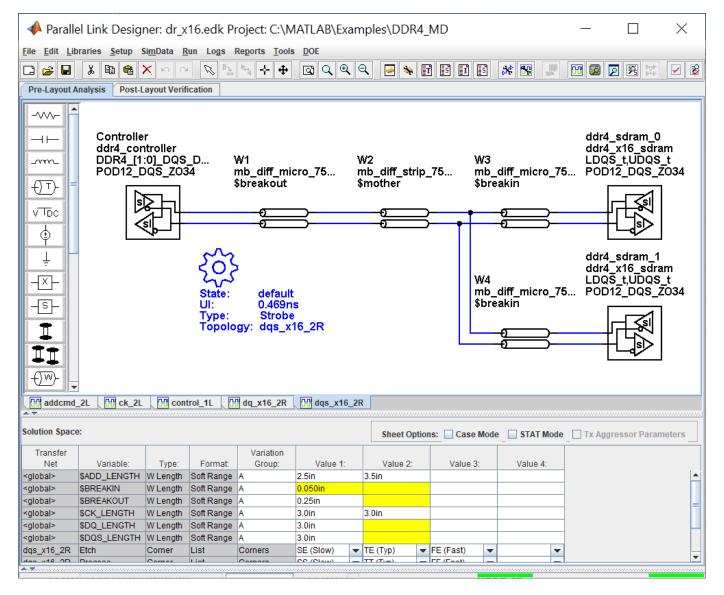

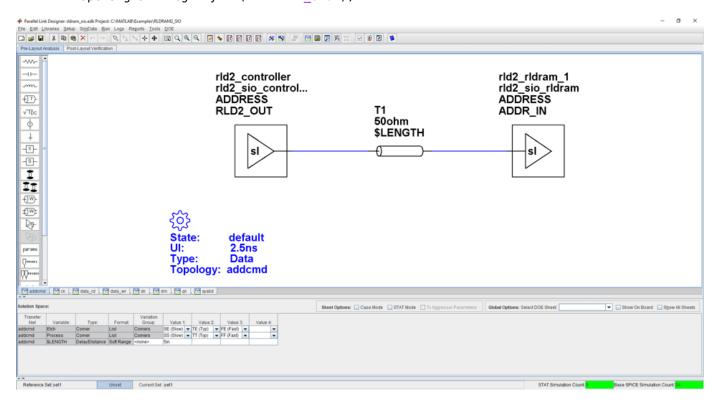

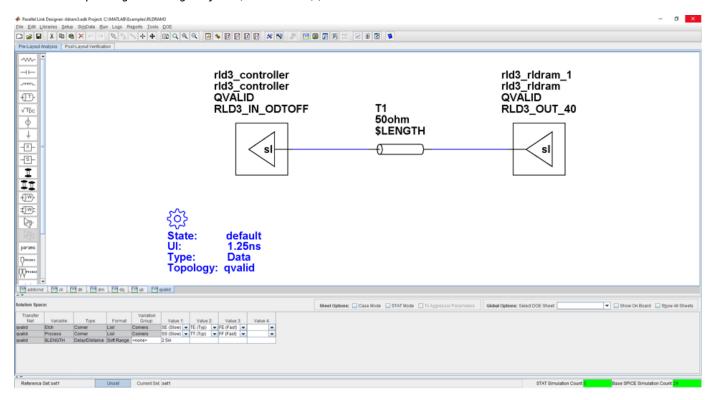

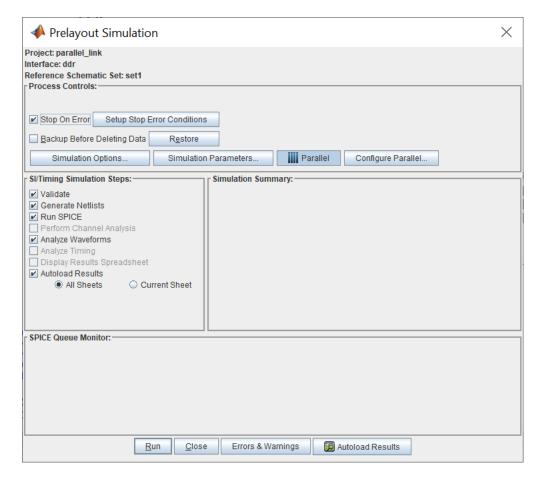

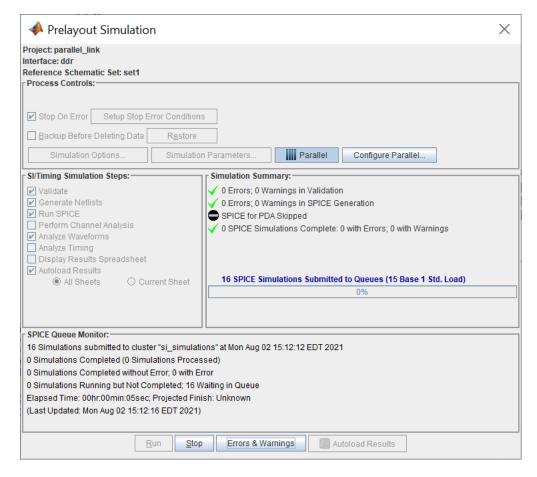

| Pre-Layout Analysis of Parallel Link                                                                                                                                                                                                                                                                                                                            |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Schematic Elements                                                                                                                                                                                                                                                                                                                                              |      |

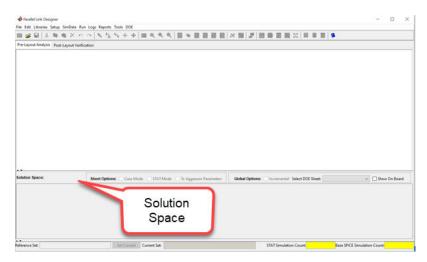

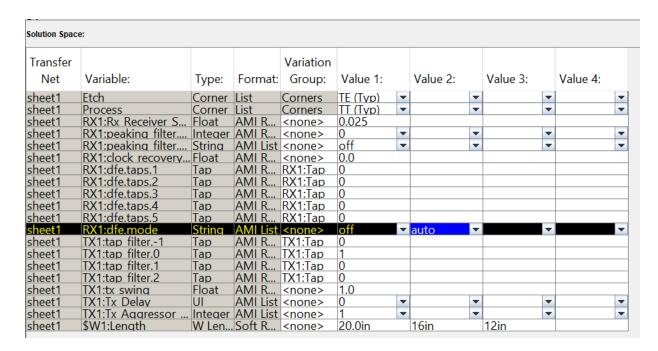

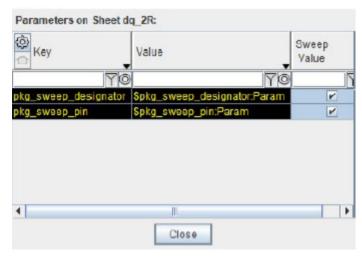

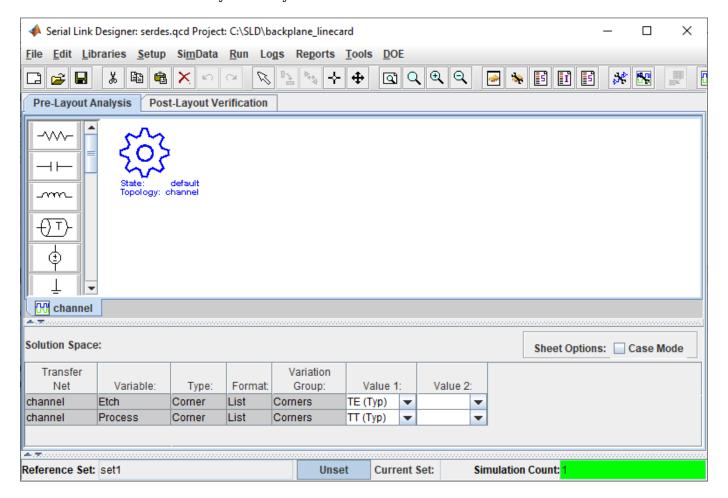

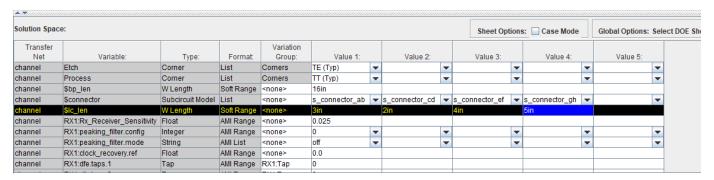

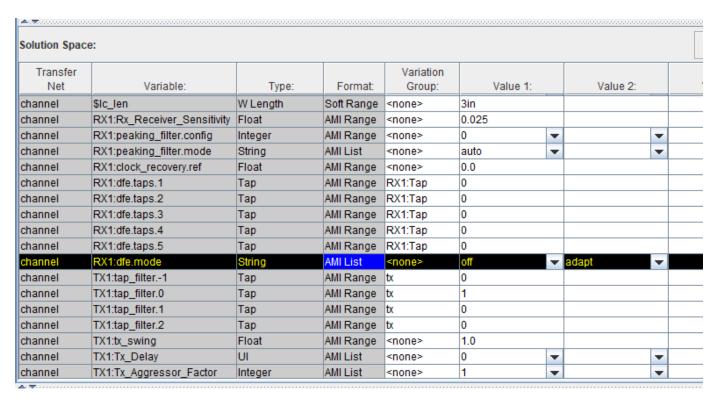

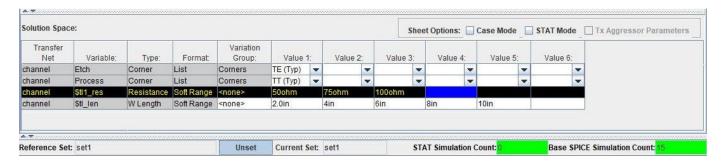

| Solution Space                                                                                                                                                                                                                                                                                                                                                  |      |

| Sheet Simulation Control                                                                                                                                                                                                                                                                                                                                        |      |

| Customize Parallel Link Project for Pre-Layout Analysis                                                                                                                                                                                                                                                                                                         |      |

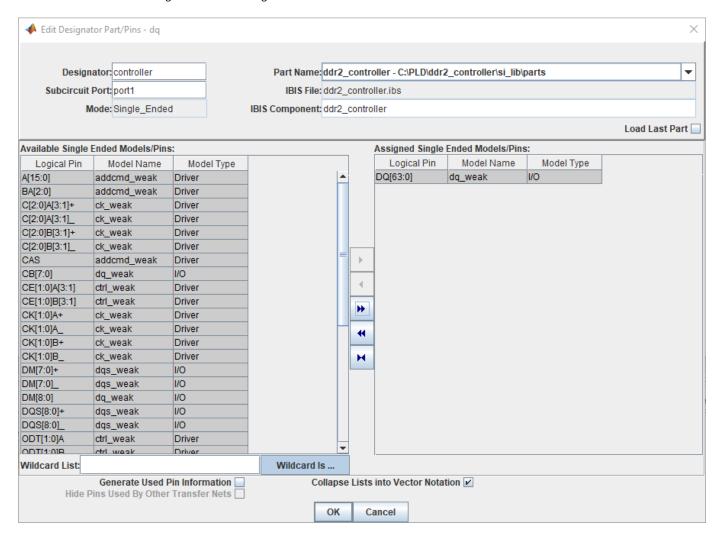

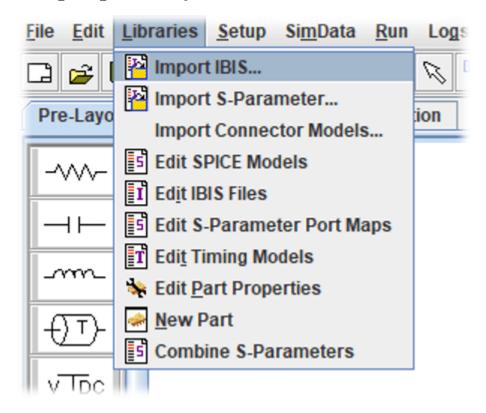

| Using I/O buffers                                                                                                                                                                                                                                                                                                                                               |      |

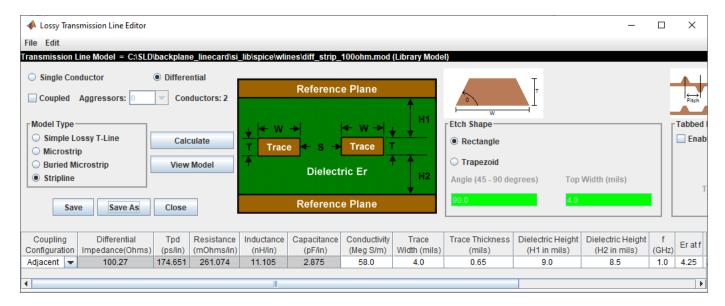

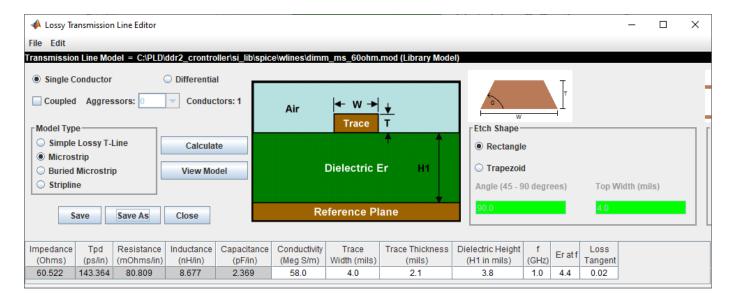

| Using Transmission Lines                                                                                                                                                                                                                                                                                                                                        |      |

| Using Vias                                                                                                                                                                                                                                                                                                                                                      |      |

| Using S-Parameters                                                                                                                                                                                                                                                                                                                                              |      |

| Using STAT Mode                                                                                                                                                                                                                                                                                                                                                 |      |

| Results of Pre-Layout Analysis in Parallel Link                                                                                                                                                                                                                                                                                                                 |      |

| Validation Reports                                                                                                                                                                                                                                                                                                                                              |      |

| Waveform and Timing Report                                                                                                                                                                                                                                                                                                                                      |      |

| Assignment Report                                                                                                                                                                                                                                                                                                                                               |      |

| SPICE Generation Report                                                                                                                                                                                                                                                                                                                                         |      |

|                                                                                                                                                                                                                                                                                                                                                                 |      |

| Post-Layout Verification of Paral                                                                                                                                                                                                                                                                                                                               | llel |

|                                                                                                                                                                                                                                                                                                                                                                 |      |

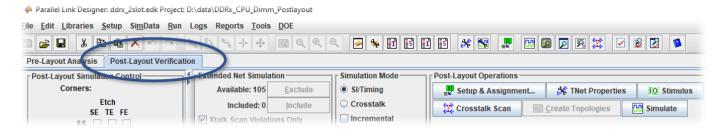

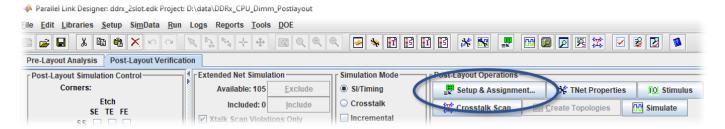

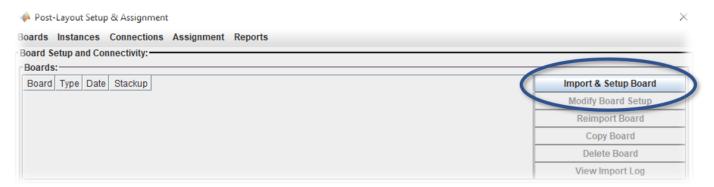

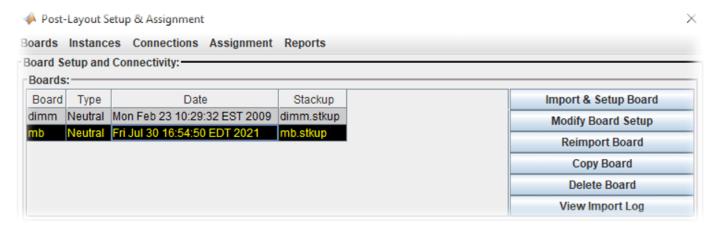

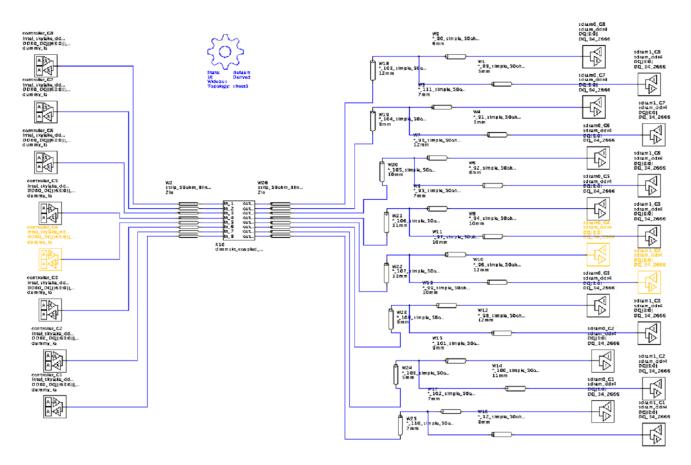

| Post-Layout Verification of Parallel Link                                                                                                                                                                                                                                                                                                                       |      |

|                                                                                                                                                                                                                                                                                                                                                                 |      |

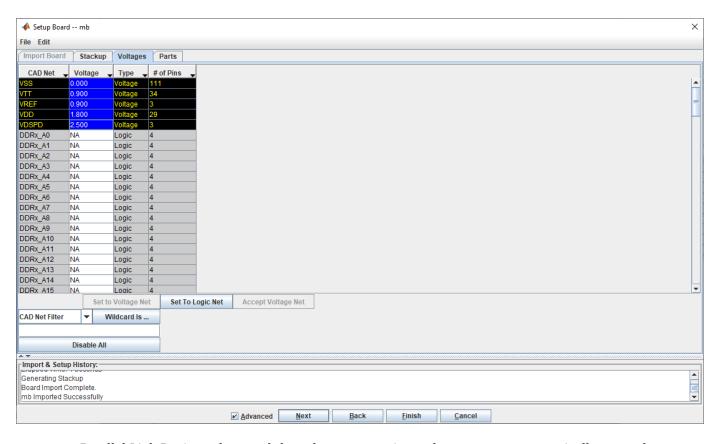

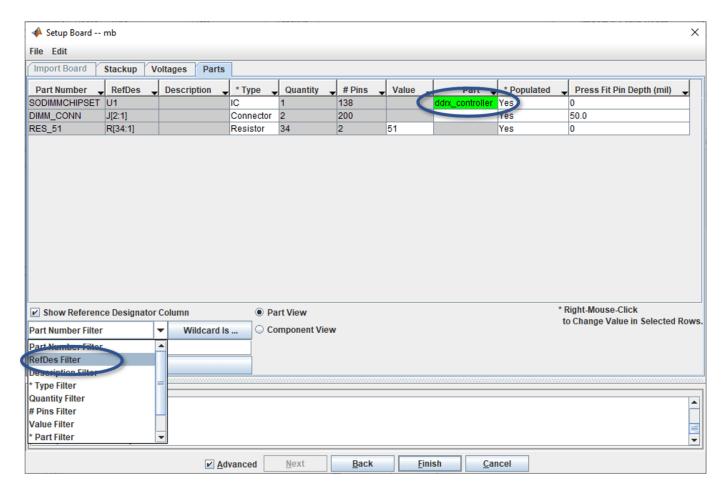

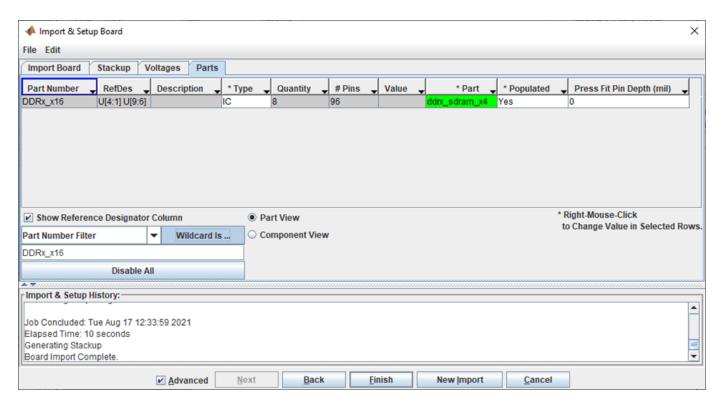

| Board                                                                                                                                                                                                                                                                                                                                                           |      |

| Board                                                                                                                                                                                                                                                                                                                                                           |      |

| Board                                                                                                                                                                                                                                                                                                                                                           |      |

| Instance                                                                                                                                                                                                                                                                                                                                                        |      |

| Board Instance Connection Assignment Population                                                                                                                                                                                                                                                                                                                 |      |

| Board Instance Connection Assignment Population Simulation                                                                                                                                                                                                                                                                                                      |      |

| Board Instance Connection Assignment Population                                                                                                                                                                                                                                                                                                                 |      |

| Board Instance Connection Assignment Population Simulation Topology  Stackup and Extraction Control in Parallel Link Project                                                                                                                                                                                                                                    |      |

| Board Instance Connection Assignment Population Simulation Topology  Stackup and Extraction Control in Parallel Link Project Stackup Editor                                                                                                                                                                                                                     |      |

| Board Instance Connection Assignment Population Simulation Topology  Stackup and Extraction Control in Parallel Link Project                                                                                                                                                                                                                                    |      |

| Board Instance Connection Assignment Population Simulation Topology  Stackup and Extraction Control in Parallel Link Project Stackup Editor Extraction Control                                                                                                                                                                                                  |      |

| Board Instance Connection Assignment Population Simulation Topology  Stackup and Extraction Control in Parallel Link Project Stackup Editor Extraction Control  Via and Stackup Management in Parallel Link Project Via Elements                                                                                                                                |      |

| Board Instance Connection Assignment Population Simulation Topology  Stackup and Extraction Control in Parallel Link Project Stackup Editor Extraction Control  Via and Stackup Management in Parallel Link Project Via Elements Editing Via for Pre-Layout Simulations                                                                                         |      |

| Board Instance Connection Assignment Population Simulation Topology  Stackup and Extraction Control in Parallel Link Project Stackup Editor Extraction Control  Via and Stackup Management in Parallel Link Project Via Elements Editing Via for Pre-Layout Simulations Editing Via for Post-Layout Simulations                                                 |      |

| Board Instance Connection Assignment Population Simulation Topology  Stackup and Extraction Control in Parallel Link Project Stackup Editor Extraction Control  Via and Stackup Management in Parallel Link Project Via Elements Editing Via for Pre-Layout Simulations Editing Via for Post-Layout Simulations Padstack Definitions                            |      |

| Board Instance Connection Assignment Population Simulation Topology  Stackup and Extraction Control in Parallel Link Project Stackup Editor Extraction Control  Via and Stackup Management in Parallel Link Project Via Elements Editing Via for Pre-Layout Simulations Editing Via for Post-Layout Simulations Padstack Definitions Padstack Editor View Modes |      |

| Board Instance Connection Assignment Population Simulation Topology  Stackup and Extraction Control in Parallel Link Project Stackup Editor Extraction Control  Via and Stackup Management in Parallel Link Project Via Elements Editing Via for Pre-Layout Simulations Editing Via for Post-Layout Simulations Padstack Definitions                            |      |

| Board Instance Connection Assignment Population Simulation Topology  Stackup and Extraction Control in Parallel Link Project Stackup Editor Extraction Control  Via and Stackup Management in Parallel Link Project Via Elements Editing Via for Pre-Layout Simulations Editing Via for Post-Layout Simulations Padstack Definitions Padstack Editor View Modes |      |

| 4 |   |   |

|---|---|---|

| 4 |   | ١ |

| 4 | ч |   |

|   |   | , |

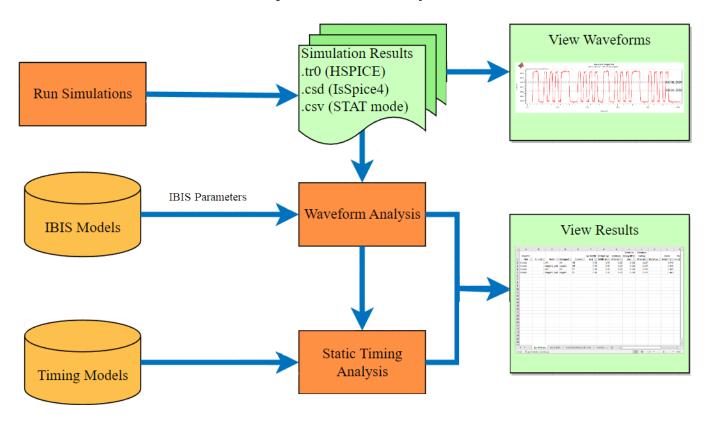

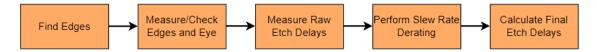

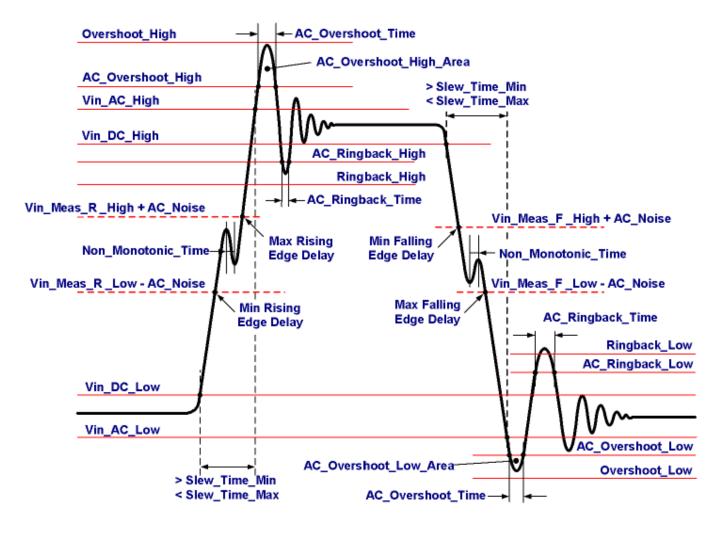

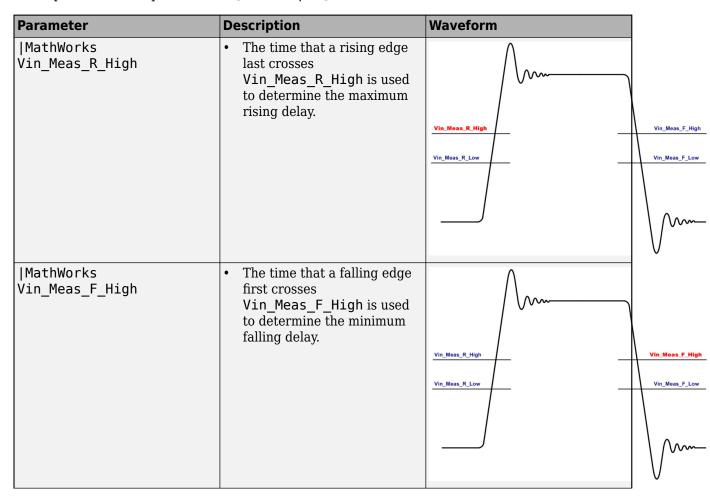

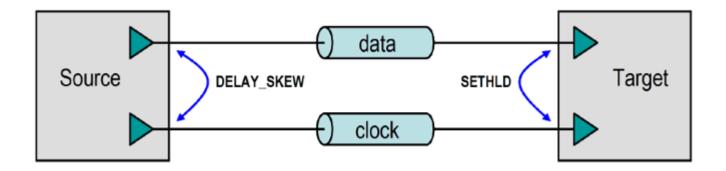

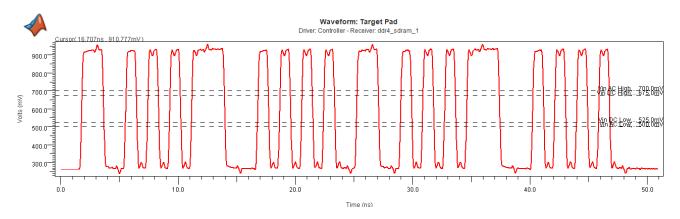

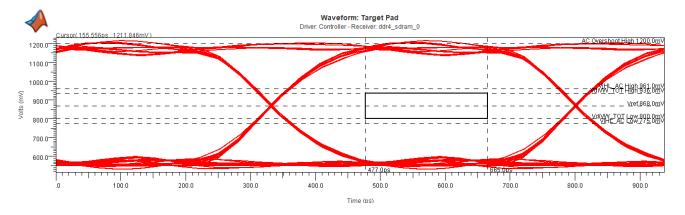

| Waveform Analysis  Transfer Net Waveform Analysis  Standard Load Waveform Analysis  Waveform Factors Affecting Interconnect Delay                                                                                                                                                                                                                | . 9-2<br>9-4                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Waveform Analysis Parameters and Thresholds  Waveform Processing Parameters  Waveform Check Parameters  Eye Measurement Parameters  Eye Check Parameters  Etch Delay Measurement Threshold Parameters  Standard Load Parameters  Other Parameters  Threshold Parameter Precedence  Waveform Reports  Waveform Analysis Report Tabs  Mask Results |                                      |

| Parallel Link Featured Exa                                                                                                                                                                                                                                                                                                                       | mples                                |

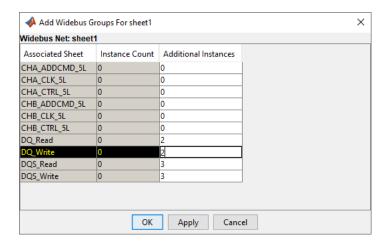

| Configure DDR Controller with Two Memory Designators                                                                                                                                                                                                                                                                                             | 10-2                                 |

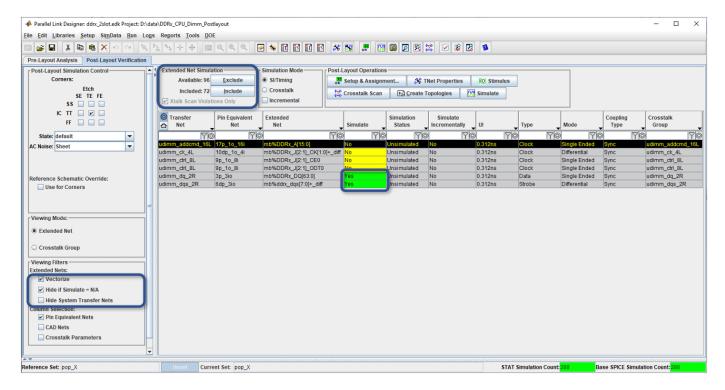

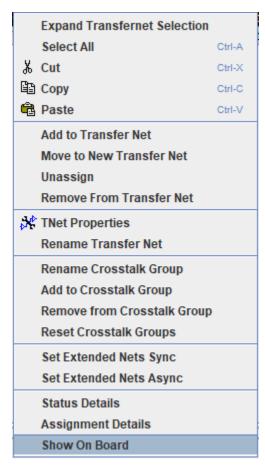

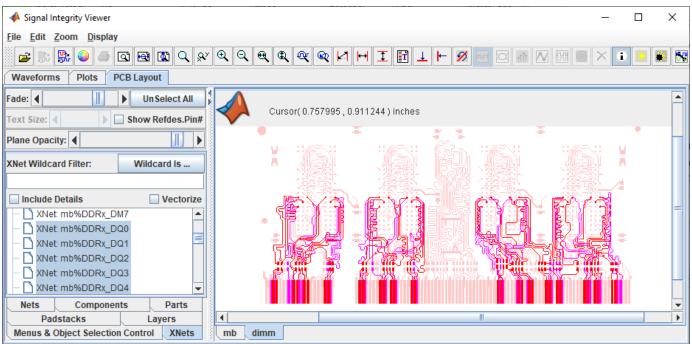

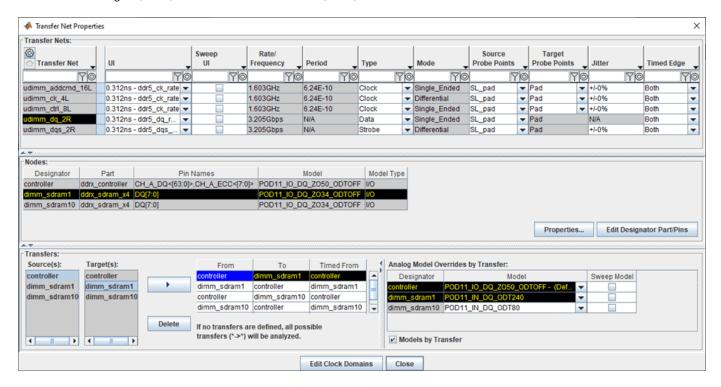

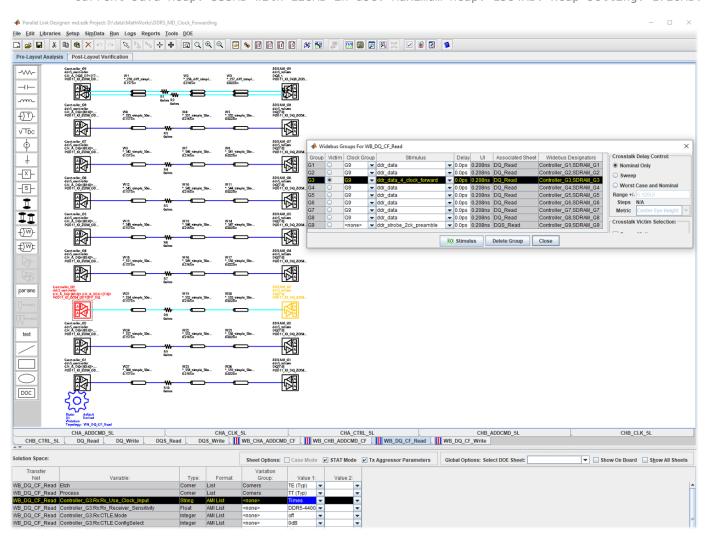

| Post-layout of DDRx Interface with CPU and DIMMs                                                                                                                                                                                                                                                                                                 | 10-8                                 |

| DDR5 IBIS-AMI with Clock Forwarding                                                                                                                                                                                                                                                                                                              | 10-30                                |

| DDRx Timing and Waveform Mask Analysis                                                                                                                                                                                                                                                                                                           | 10-32                                |

| Jitter and                                                                                                                                                                                                                                                                                                                                       | Noise                                |

| Model Jitter and Noise While Designing Parallel Link  TX Clock Jitter  RX Clock Jitter  RX Clock Recovery Jitter  RX Noise  Set Jitter and Noise in AMI File                                                                                                                                                                                     | 11-2<br>11-2<br>11-4<br>11-6<br>11-7 |

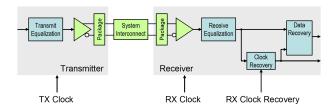

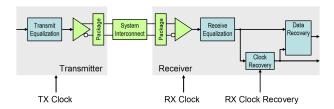

| Model Jitter and Noise While Designing Serial Link TX Clock Jitter RX Clock Jitter RX Clock Recovery Jitter                                                                                                                                                                                                                                      | 11-9<br>11-9<br>11-11                |

## **Industry Standard Examples**

| 7 |   |

|---|---|

|   |   |

|   | _ |

| 10GBASE-KR4 Compliance Kit               | <b>12-</b> 3  |

|------------------------------------------|---------------|

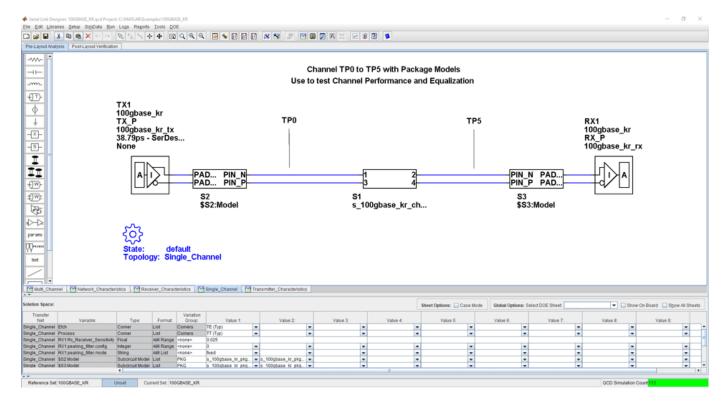

| 100GBASE-KR4 Compliance Kit              | <b>12-</b> 5  |

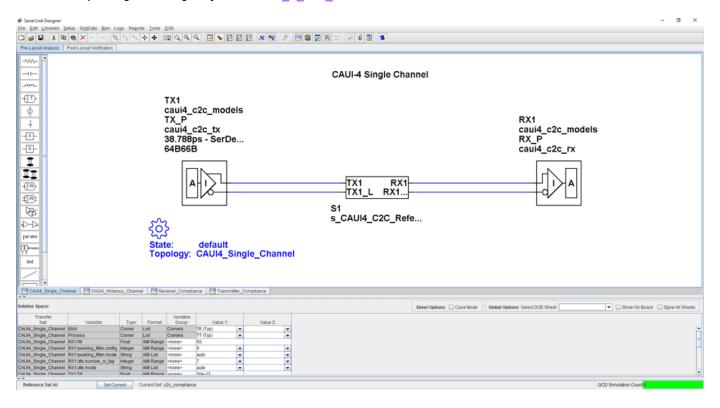

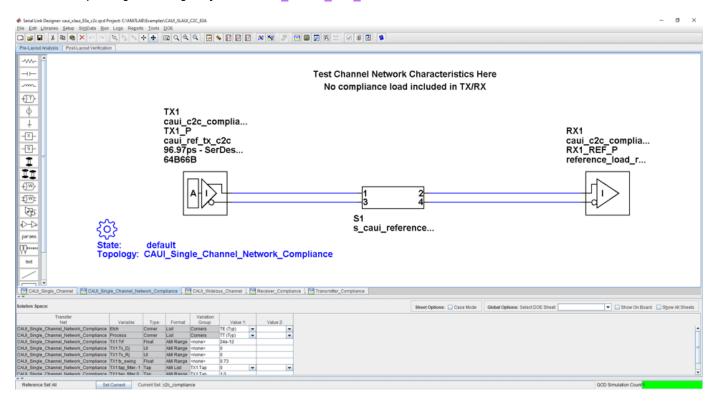

| CAUI-4 Chip-to-Chip Compliance Kit       | 12-7          |

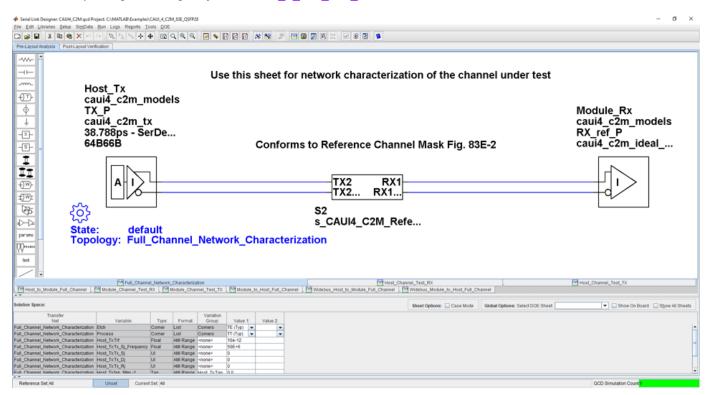

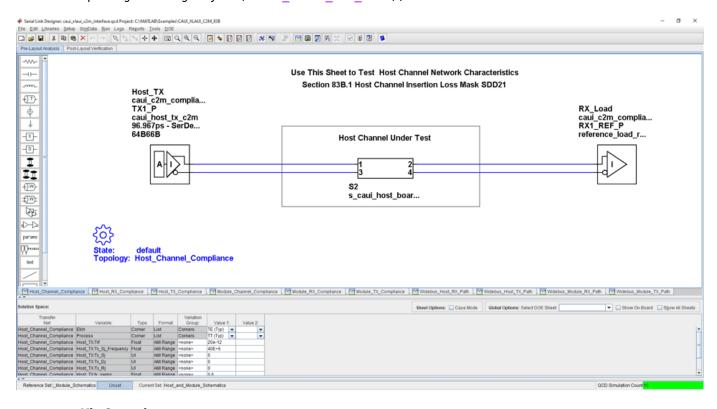

| CAUI-4 Chip-to-Module Compliance Kit     | 12-9          |

| CAUI/XLAUI Chip-to-Chip Compliance Kit   | 12-11         |

| CAUI/XLAUI Chip-To-Module Compliance Kit | <b>12-1</b> 3 |

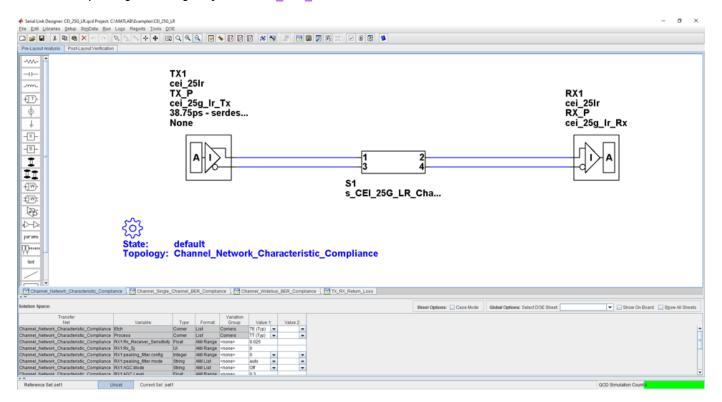

| CEI 25G-LR Compliance Kit                | 12-15         |

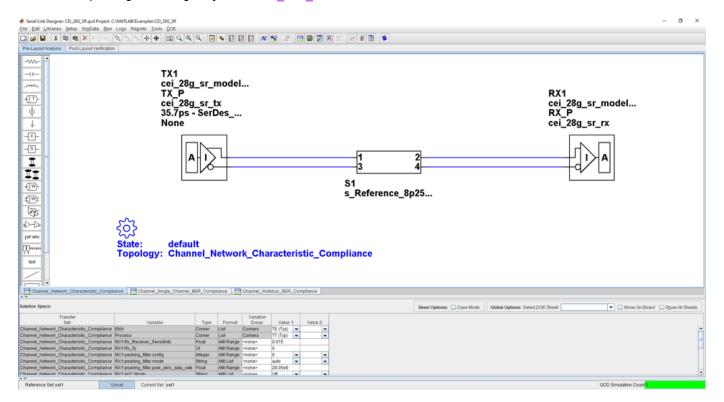

| CEI 28G-SR Compliance Kit                | 12-17         |

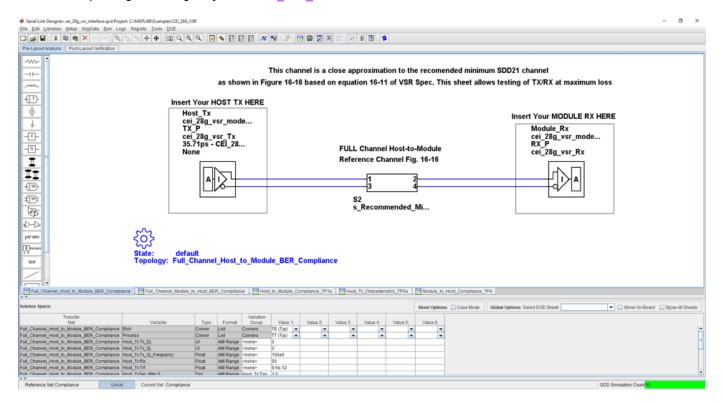

| CEI 28G-VSR Compliance Kit               | 12-19         |

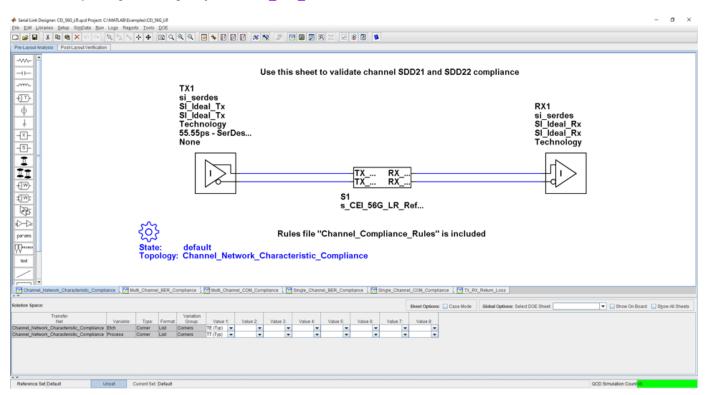

| CEI 56G-LR Compliance Kit                | 12-21         |

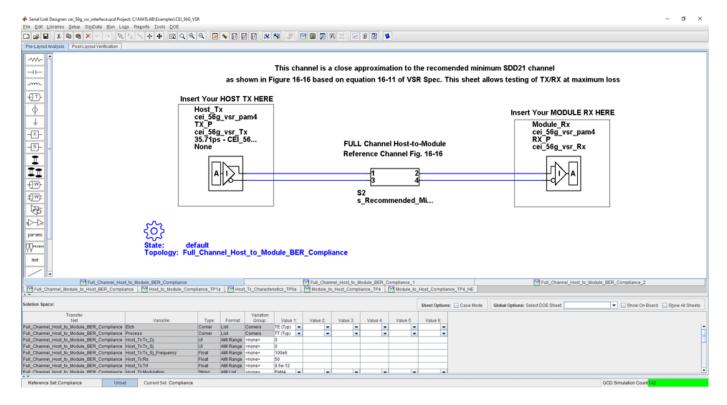

| CEI 56G-VSR Compliance Kit               | <b>12-2</b> 3 |

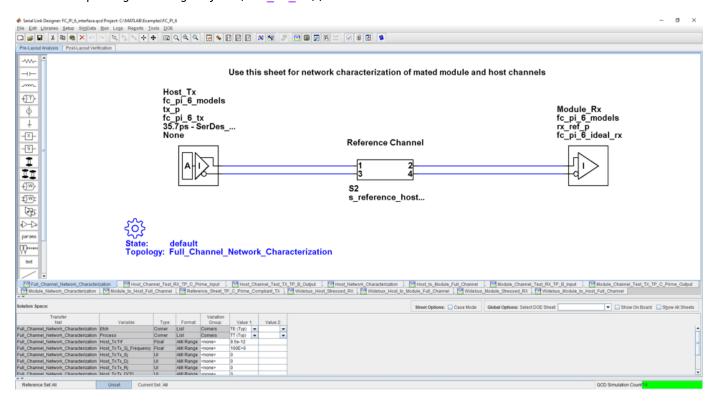

| Fibre Channel FC-PI-6 Compliance Kit     | 12-25         |

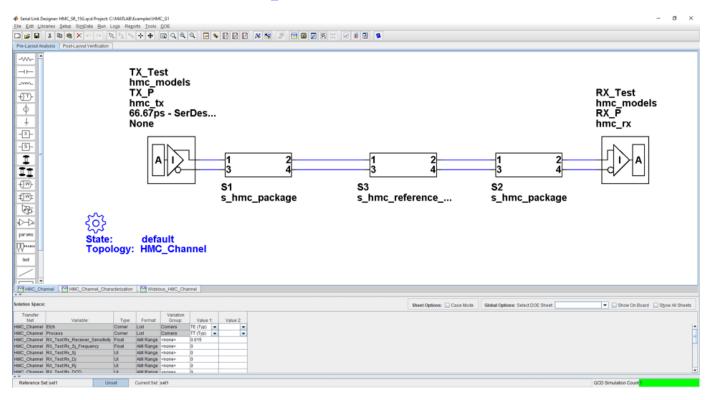

| HMC 15G-SR Compliance Kit                | 12-27         |

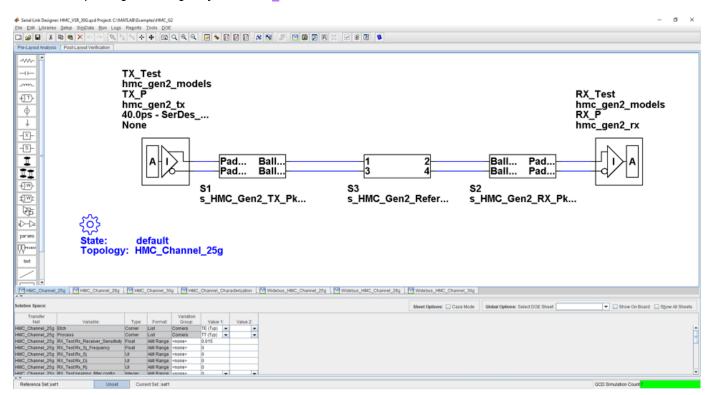

| HMC 30G-VSR Compliance Kit               | 12-29         |

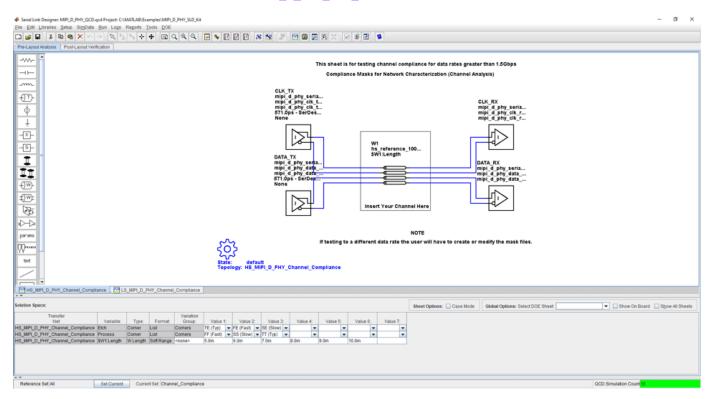

| MIPI D-PHY Serial Link Compliance Kit    | 12-31         |

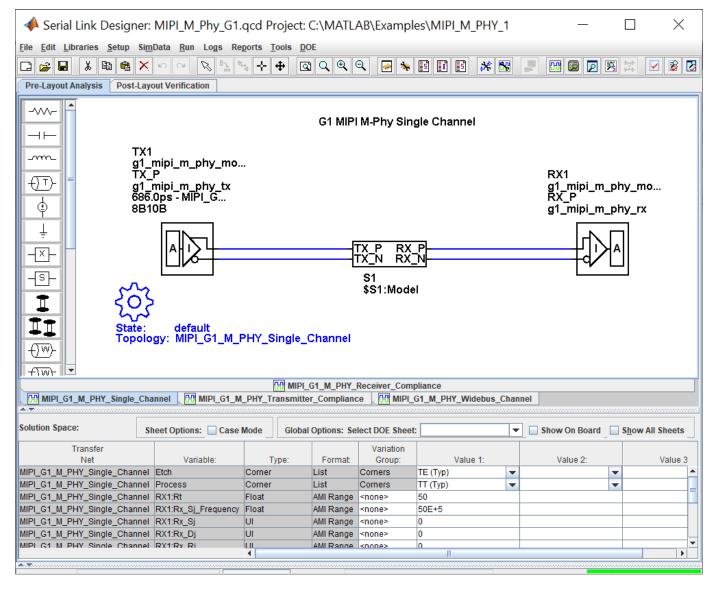

| MIPI M-PHY Compliance Kit                | <b>12-3</b> 3 |

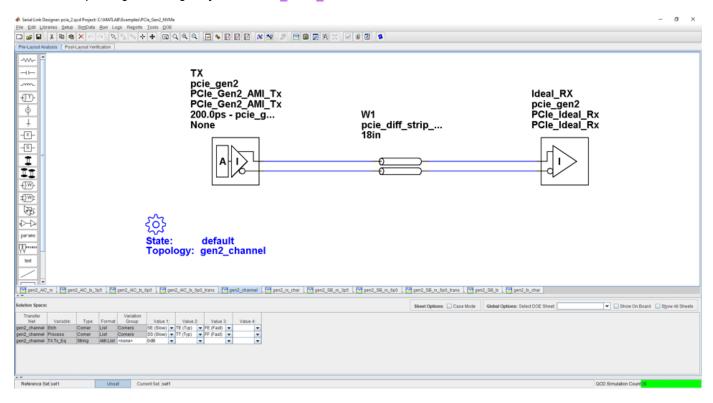

| PCIe-2 Compliance Kit                    | 12-36         |

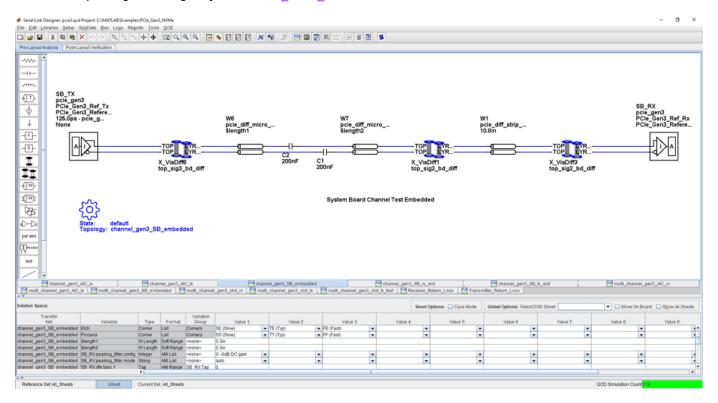

| PCIe-3 Compliance Kit                    | 12-38         |

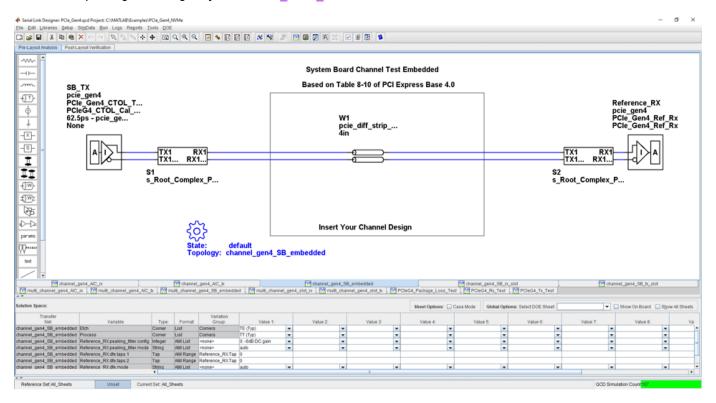

| PCIe-4 Compliance Kit                    | 12-40         |

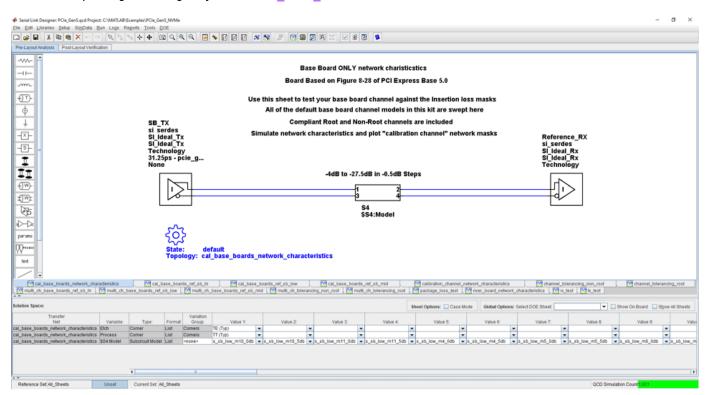

| PCIe-5 Compliance Kit                    | 12-42         |

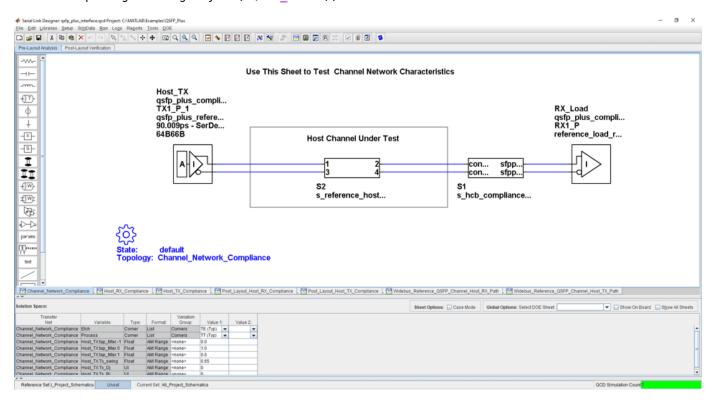

| QSFP+ Compliance Kit                     | 12-44         |

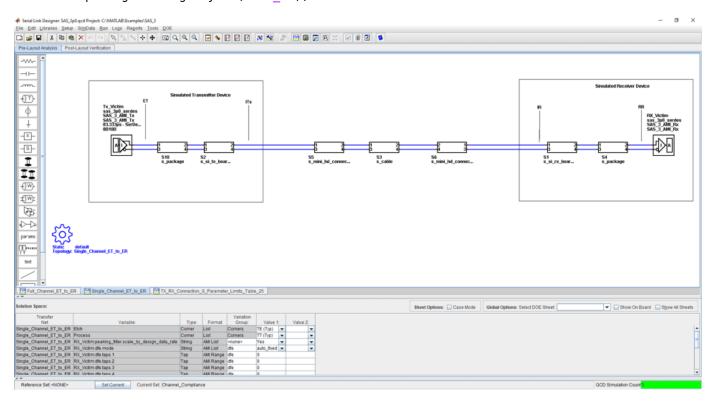

| SAS 3.0 Compliance Kit                   | 12-46         |

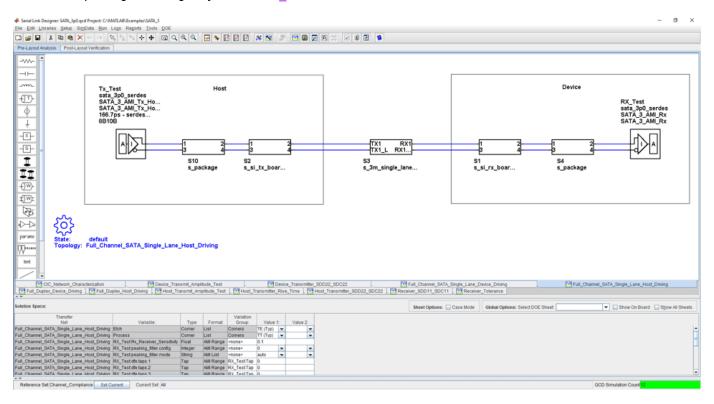

| SATA 3.0 Compliance Kit                  | 12-48         |

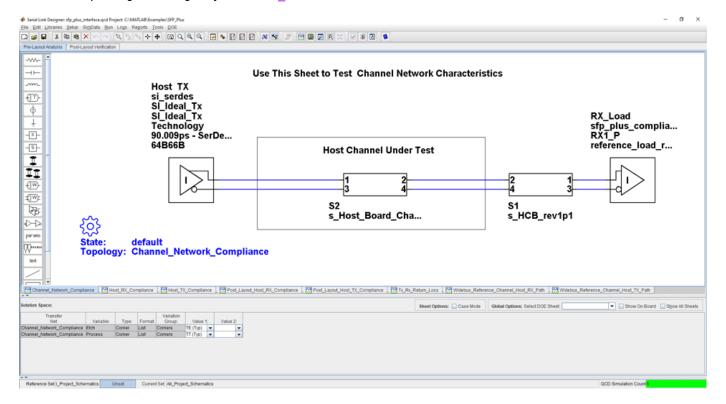

| SFP+ Compliance Kit                                                                                                                                                                           | 12-50                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

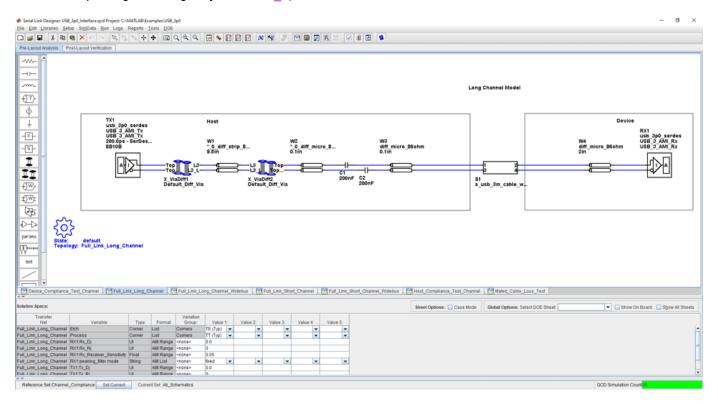

| USB 3.0 Compliance Kit                                                                                                                                                                        | 12-52                            |

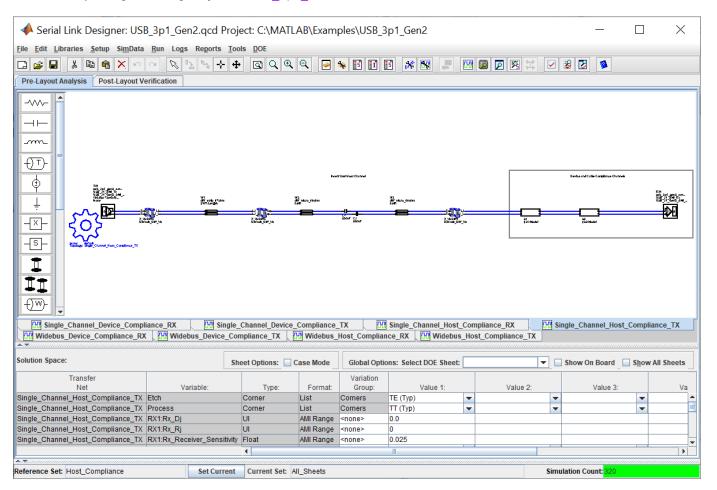

| USB 3.1 Compliance Kit                                                                                                                                                                        | 12-54                            |

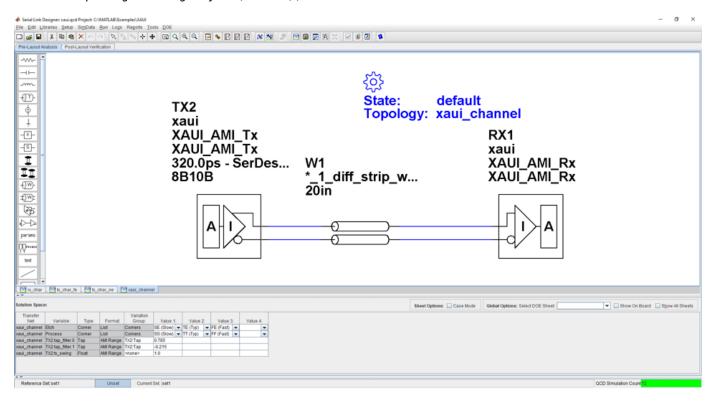

| XAUI Compliance Kit                                                                                                                                                                           | 12-56                            |

| Registered DDR2 Architectural Kit                                                                                                                                                             | 12-58                            |

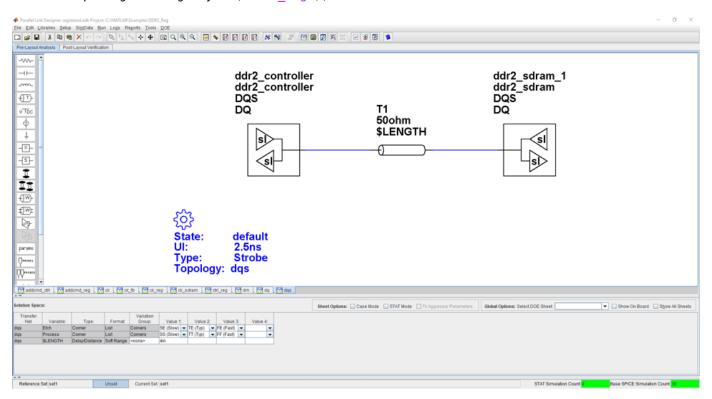

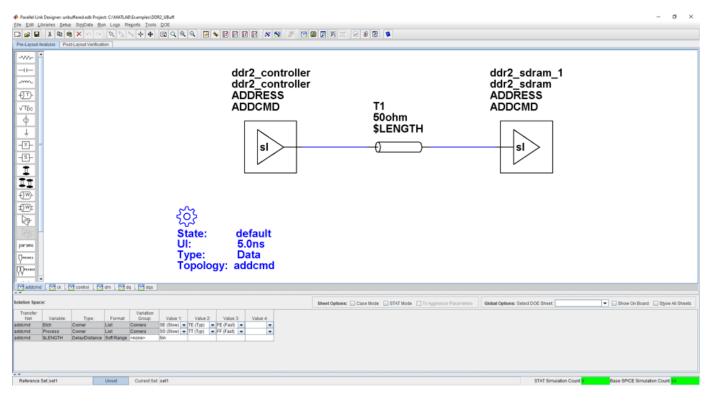

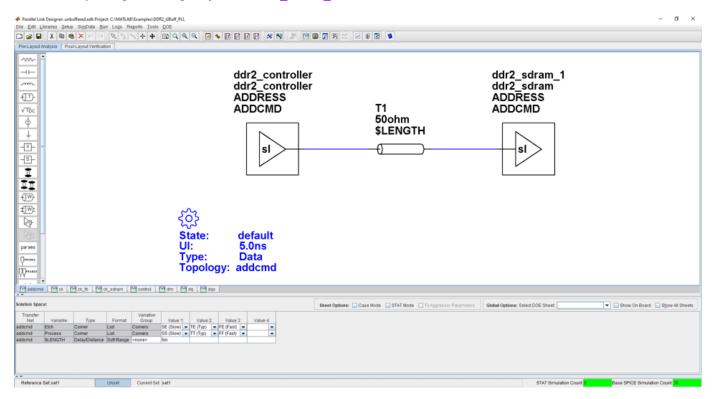

| Unbuffered DDR2 Architectural Kit                                                                                                                                                             | 12-59                            |

| Unbuffered DDR2 with PLL Architectural Kit                                                                                                                                                    | 12-60                            |

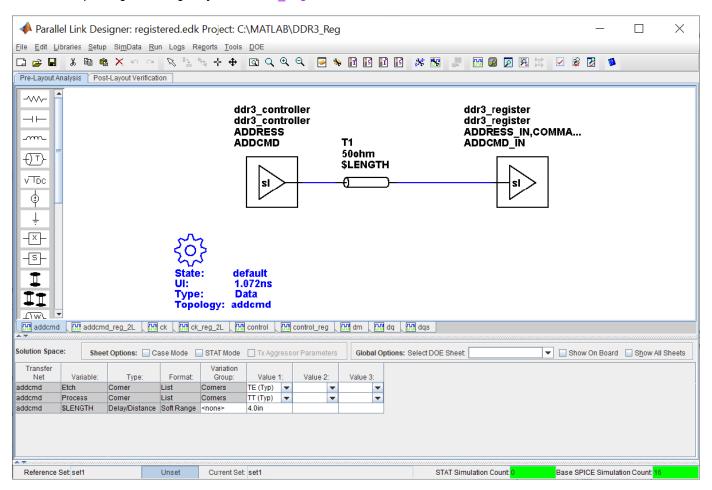

| Registered DDR3 Architectural Kit                                                                                                                                                             | 12-62                            |

| Unbuffered DDR3 Architectural Kit                                                                                                                                                             | 12-64                            |

| Unbuffered DDR3L Architectural Kit                                                                                                                                                            | 12-66                            |

| DDR4 Implementation Kit for JEDEC Raw Card B                                                                                                                                                  | 12-68                            |

| DDR4 Memory Down Implementation Kit                                                                                                                                                           | 12-71                            |

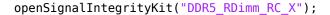

| DDR5 Implementation Kit                                                                                                                                                                       | 12-73                            |

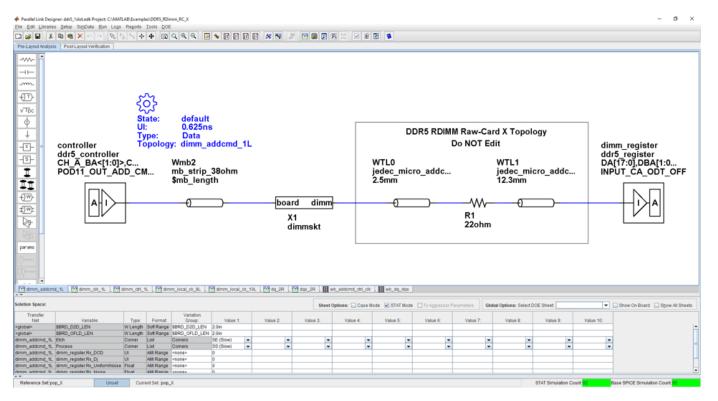

| GDDR5 x32 Implementation Kit                                                                                                                                                                  | 12-75                            |

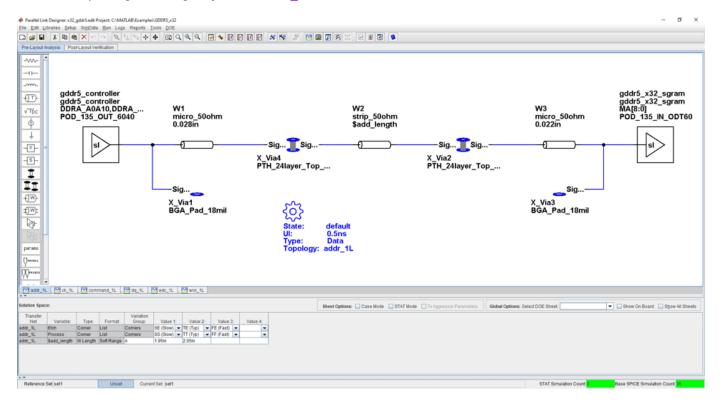

| GDDR6 x32 Architectural Kit                                                                                                                                                                   | 12-77                            |

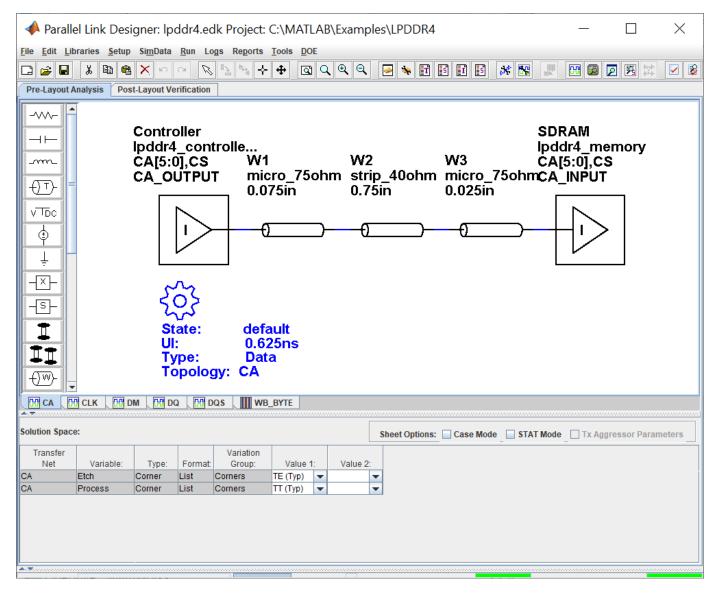

| Low-Power DDR4 Architectural Kit                                                                                                                                                              | 12-80                            |

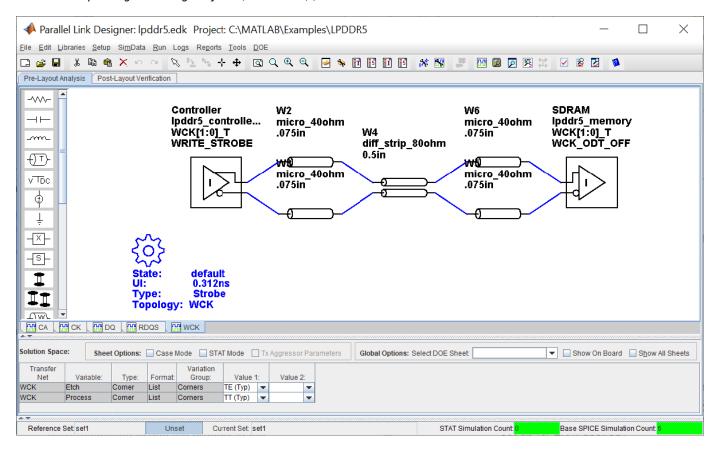

| Low-Power DDR5 Architectural Kit                                                                                                                                                              | 12-82                            |

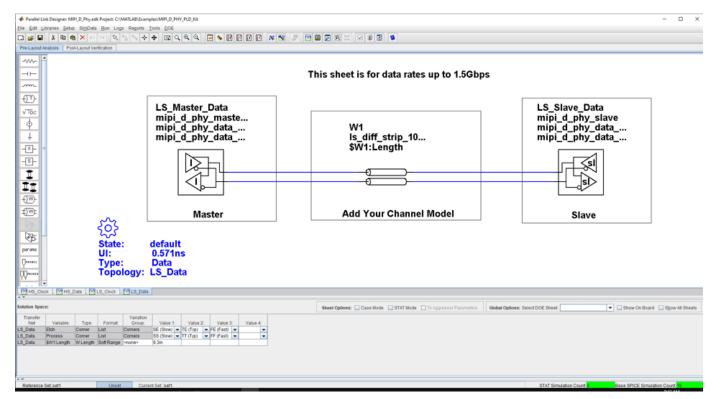

| MIPI D-PHY Parallel Link Compliance Kit                                                                                                                                                       | 12-84                            |

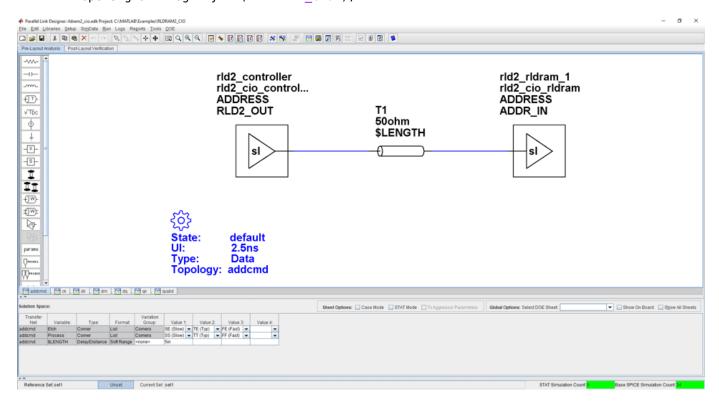

| CIO RLDRAM II Architectural Kit                                                                                                                                                               | 12-86                            |

| SIO RLDRAM II Architectural Kit                                                                                                                                                               | 12-88                            |

| RLDRAM III Architectural Kit                                                                                                                                                                  | 12-90                            |

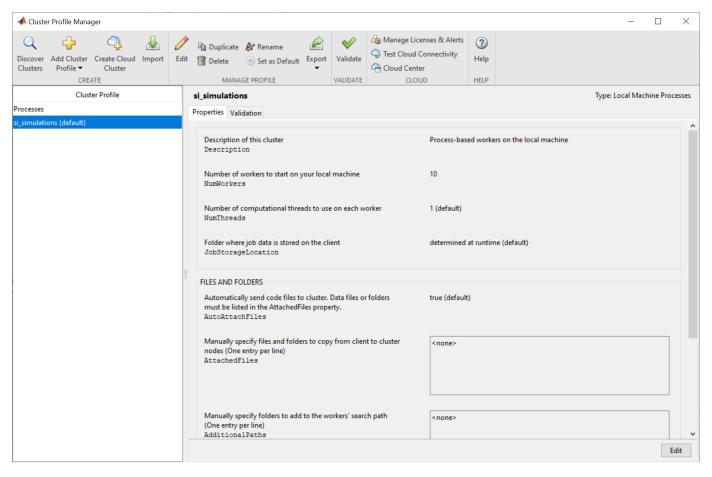

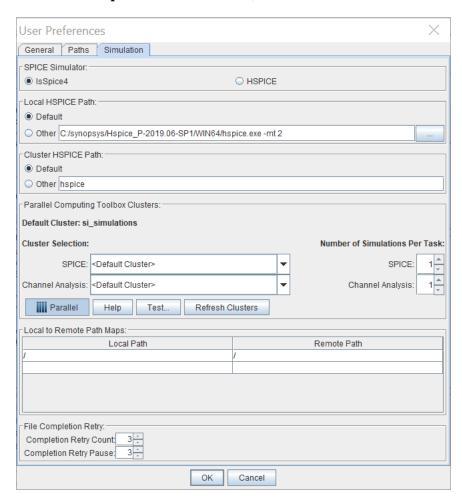

| Run Parallel Simulations in Signal Integrity Toolbox  Configure Local MATLAB Cluster for Parallel Simulations  Adjust Cluster Settings for Signal Integrity Toolbox  Run Parallel Simulations | 12-92<br>12-92<br>12-94<br>12-96 |

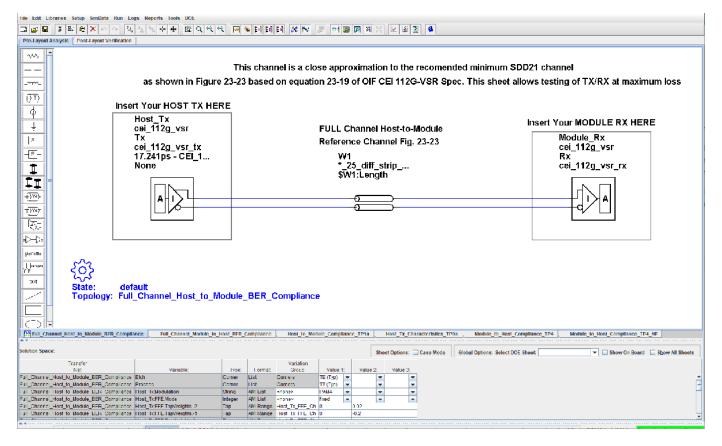

| CEL 112G-VSR Compliance Kit                                                                                                                                                                   | 12-99                            |

## **13**

| Clock Modes                                                                                                                                                                                 | 13-2                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

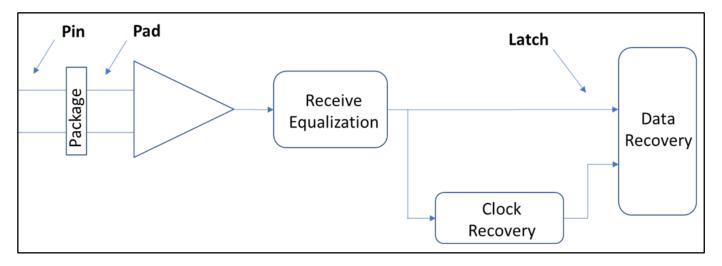

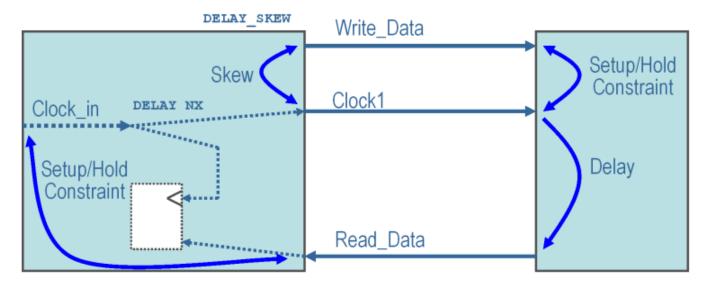

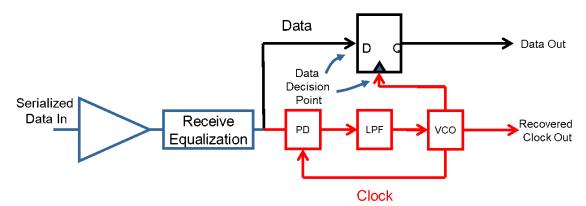

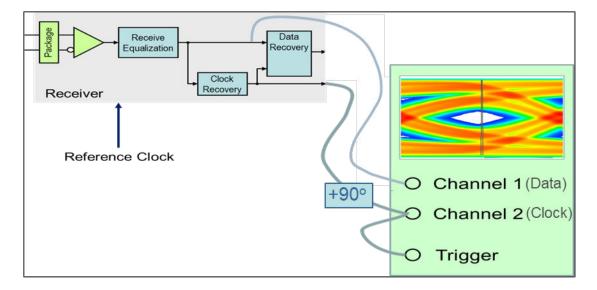

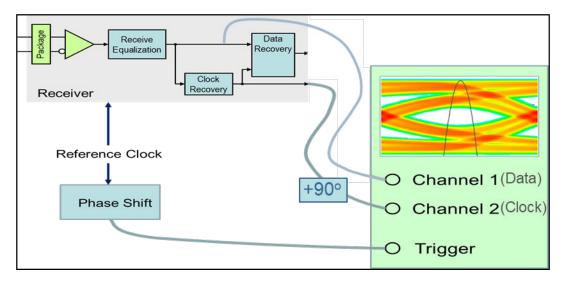

| Clock and Data Paths in Serial Link Receiver                                                                                                                                                | <b>13-</b> 2                     |

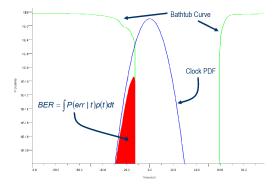

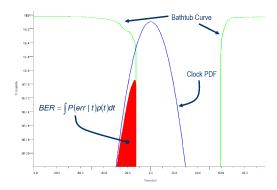

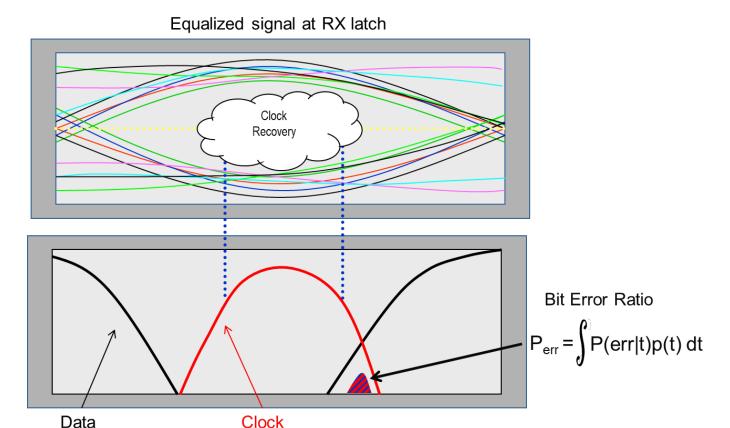

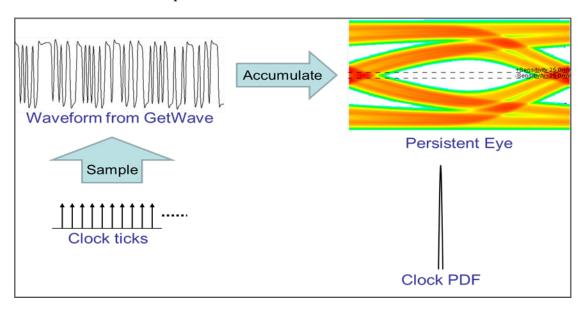

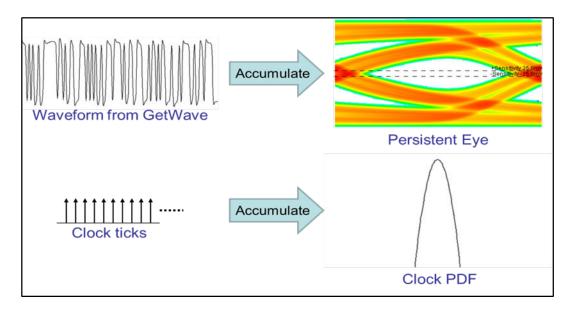

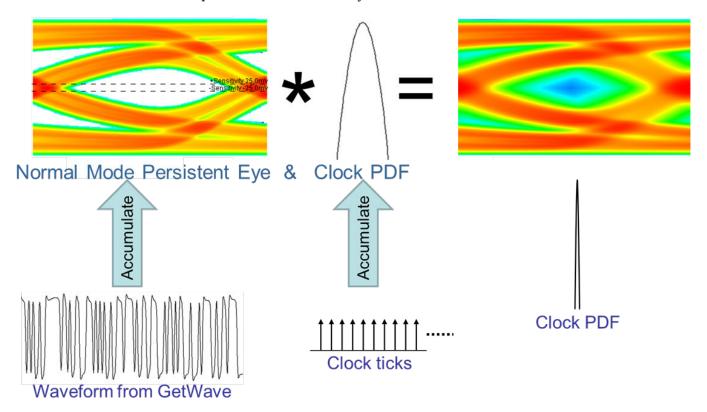

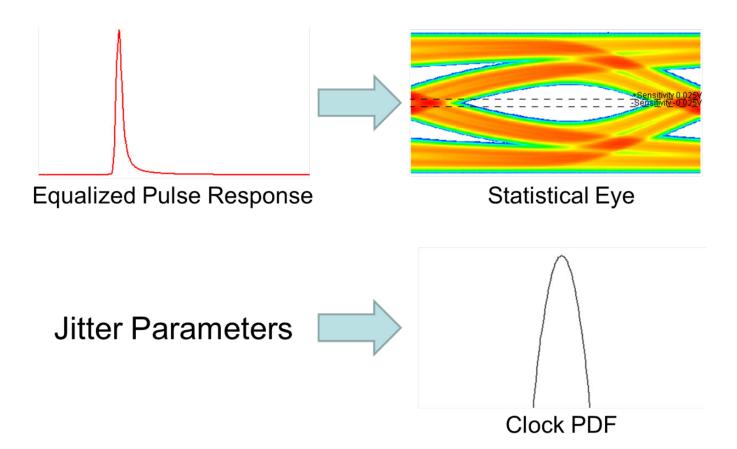

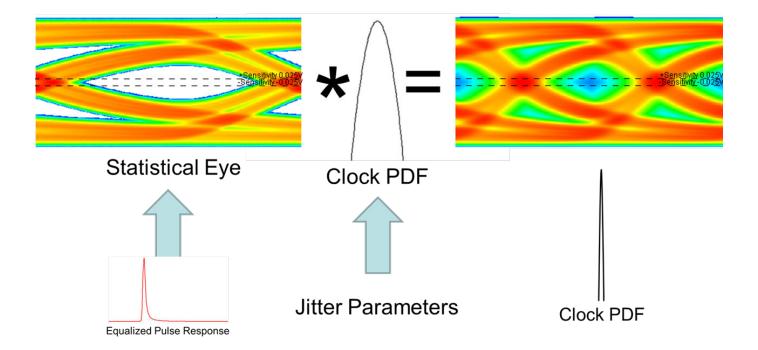

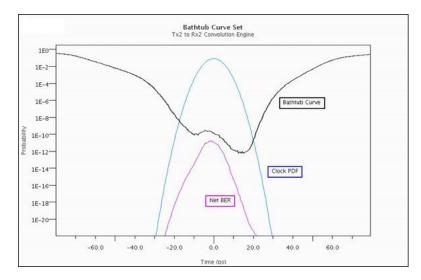

| Using Data and Clock Distribution to Predict Bit-Error Rate                                                                                                                                 | <b>13-</b> 3                     |

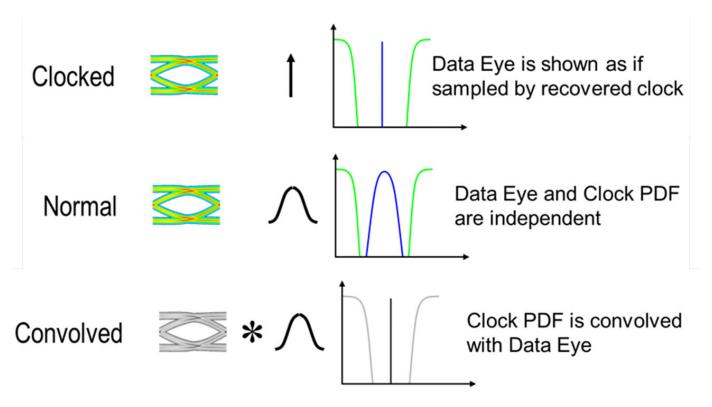

| Clock Modes                                                                                                                                                                                 | <b>13-</b> 4                     |

| Time Domain Clock Mode: Clocked                                                                                                                                                             | <b>13-</b> 4                     |

| Time Domain Clock Mode: Normal                                                                                                                                                              | 13-6                             |

| Time Domain Clock Mode: Convolved                                                                                                                                                           | 13-8                             |

| Statistical Simulations and Clock Modes                                                                                                                                                     | 13-8                             |

| Setting Clock Mode                                                                                                                                                                          | 13-10                            |

| 5000 <b></b> g 5200 <b></b> 120 <b>.</b> 170                                                                                                                                                |                                  |

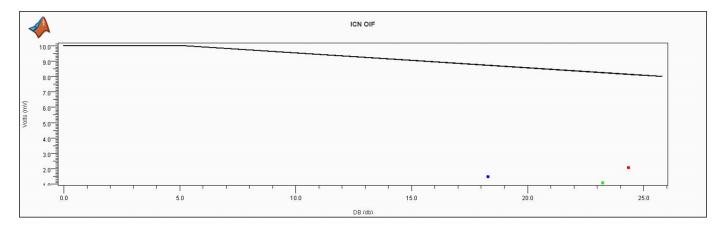

| Channel Operating Margin (COM)                                                                                                                                                              | 13-11                            |

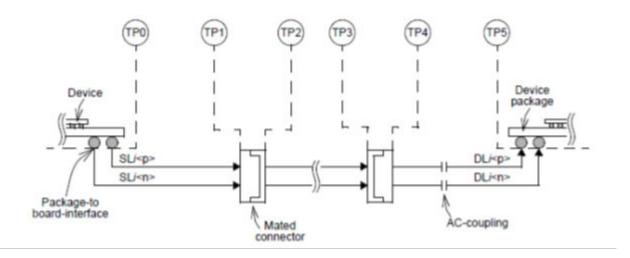

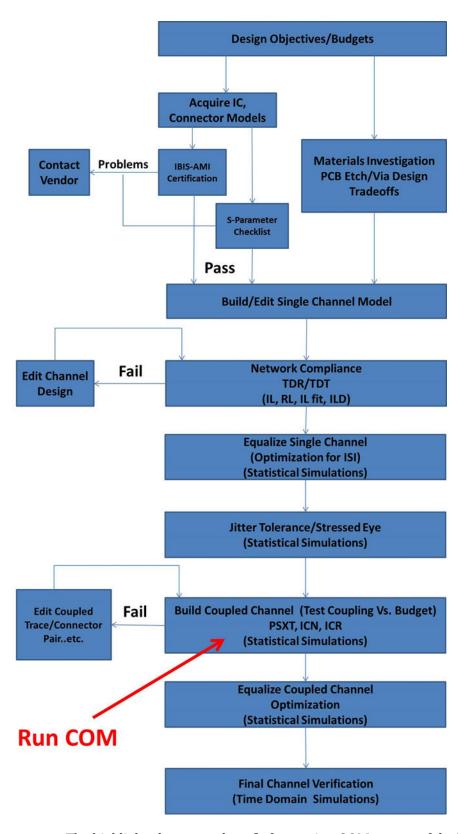

| Channel Design Methodology                                                                                                                                                                  | 13-12                            |

| COM Setup                                                                                                                                                                                   | 13-14                            |

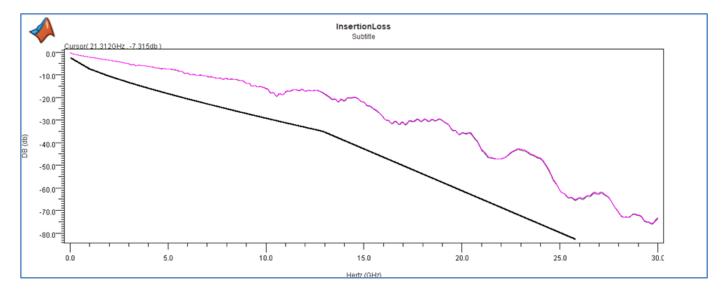

| Channel S-parameters for COM                                                                                                                                                                | 13-14                            |

| Viewing COM Results                                                                                                                                                                         | 13-15                            |

| viewing Cori Results                                                                                                                                                                        | 15-10                            |

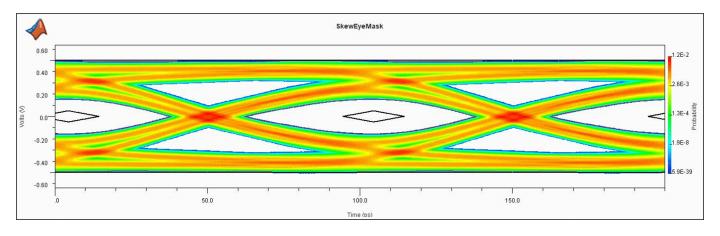

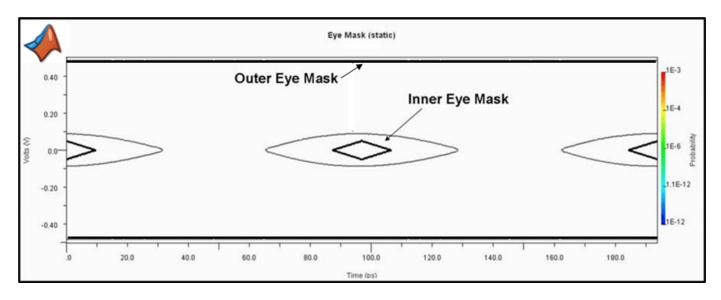

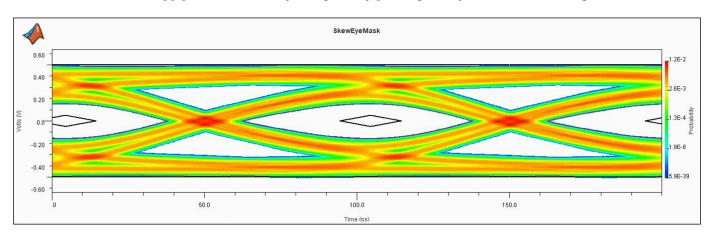

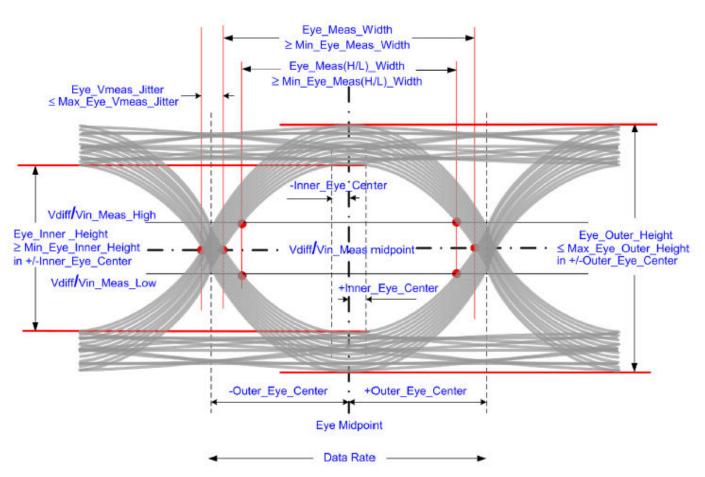

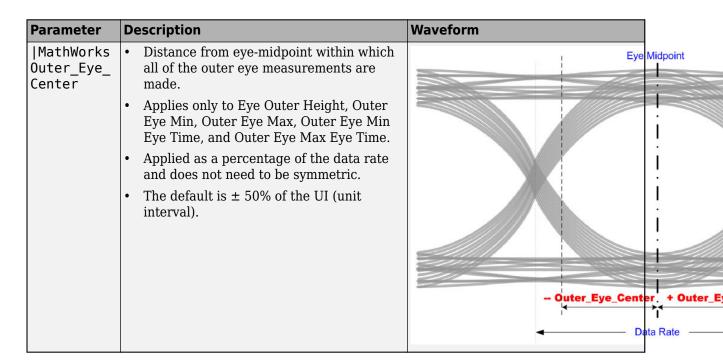

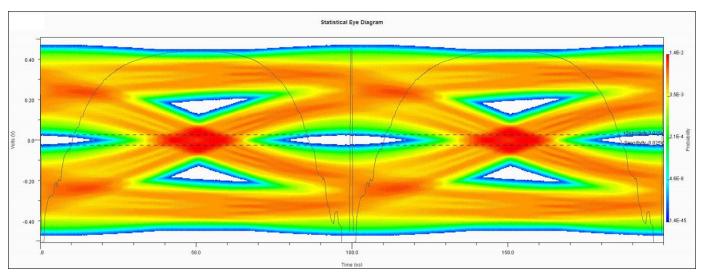

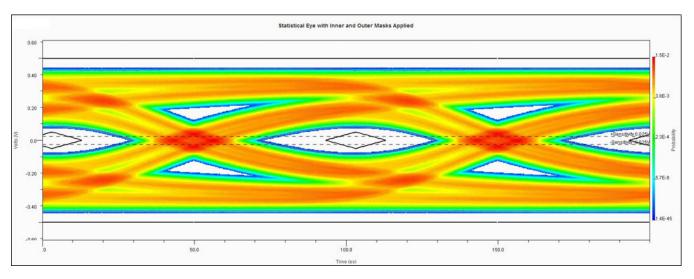

| Eye Measurement and Reporting                                                                                                                                                               | 13-17                            |

| Parameters Used in Eye Measurement                                                                                                                                                          | 13-17                            |

| Eye Reporting                                                                                                                                                                               | 13-18                            |

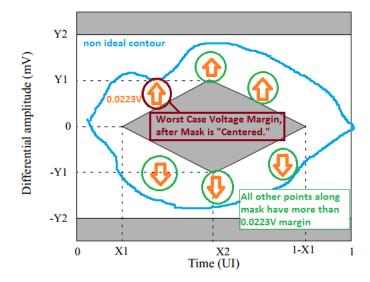

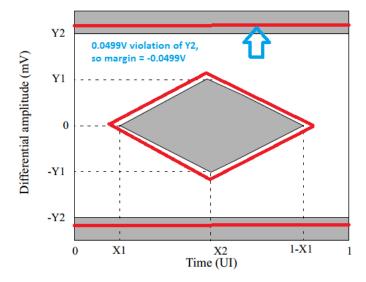

| Calculating Eye Margin from Simulation Results to Eye Mask                                                                                                                                  | 13-10                            |

| Outcomeding Lyo Plangin from Officiation Results to Lyo Plank                                                                                                                               | 10 21                            |

| Elements in Link Designer Apps                                                                                                                                                              | 13-24                            |

|                                                                                                                                                                                             |                                  |

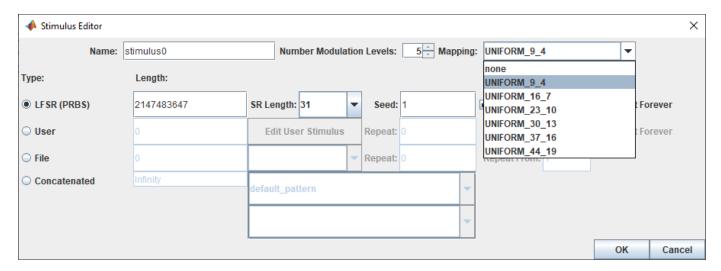

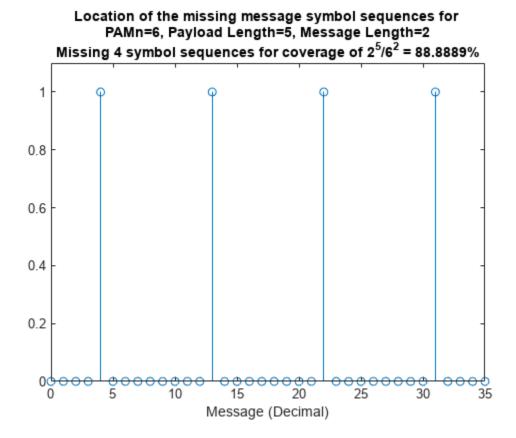

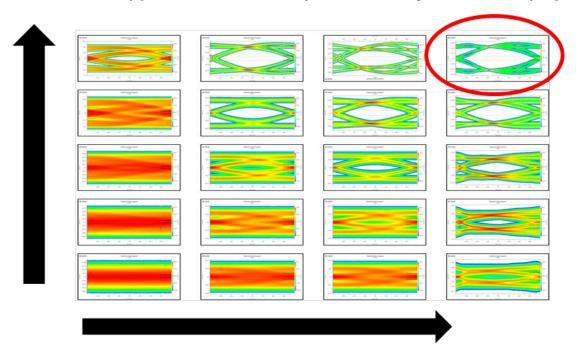

| PAMn Capabilities                                                                                                                                                                           | 13-29                            |